The STM32 Cortex-M0 instruction set PM0215

38/91 Doc ID 022979 Rev 1

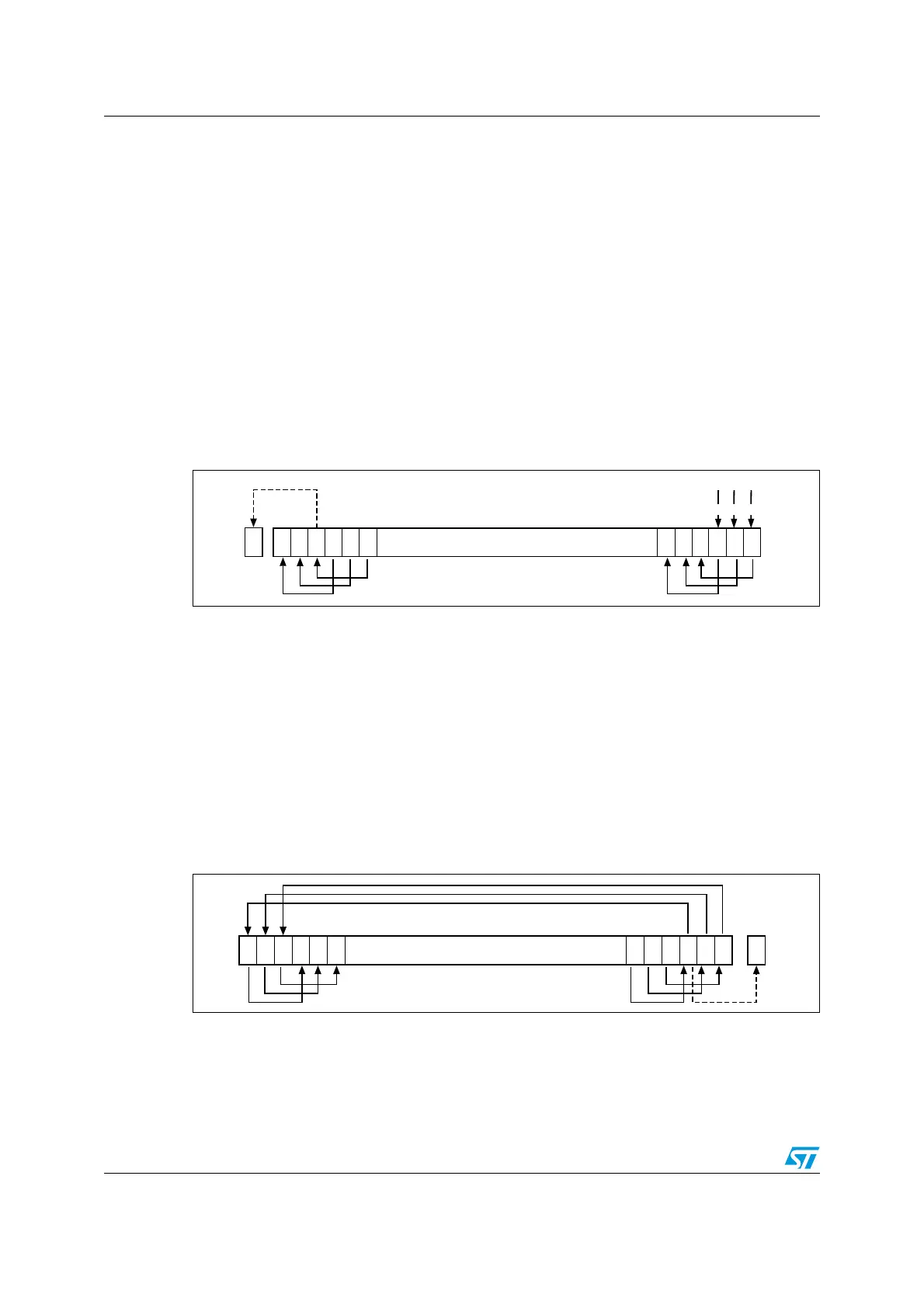

LSL

Logical shift left by

n

bits moves the right-hand

32

-

n

bits of the register

Rm

, to the left by

n

places, into the left-hand

32

-

n

bits of the result. And it sets the right-hand

n

bits of the result

to 0 (see Figure 12: LSL#3 on page 38).

You can use the LSL #n operation to multiply the value in the register

Rm

by 2

n

, if the value

is regarded as an unsigned integer or a two’s complement signed integer. Overflow can

occur without warning.

When the instruction is

LSLS

or when

LSL #n

, with non-zero

n

, is used in

operand2

with the

instructions MOVS, MVNS, ANDS, ORRS, ORNS, EORS, BICS, TEQ or TST, the carry flag

is updated to the last bit shifted out, bit[

32

-

n

], of the register

Rm

. These instructions do not

affect the carry flag when used with LSL #0.

Note: 1 If

n

is 32 or more, then all the bits in the result are cleared to 0.

2If

n

is 33 or more and the carry flag is updated, it is updated to 0.

Figure 12. LSL#3

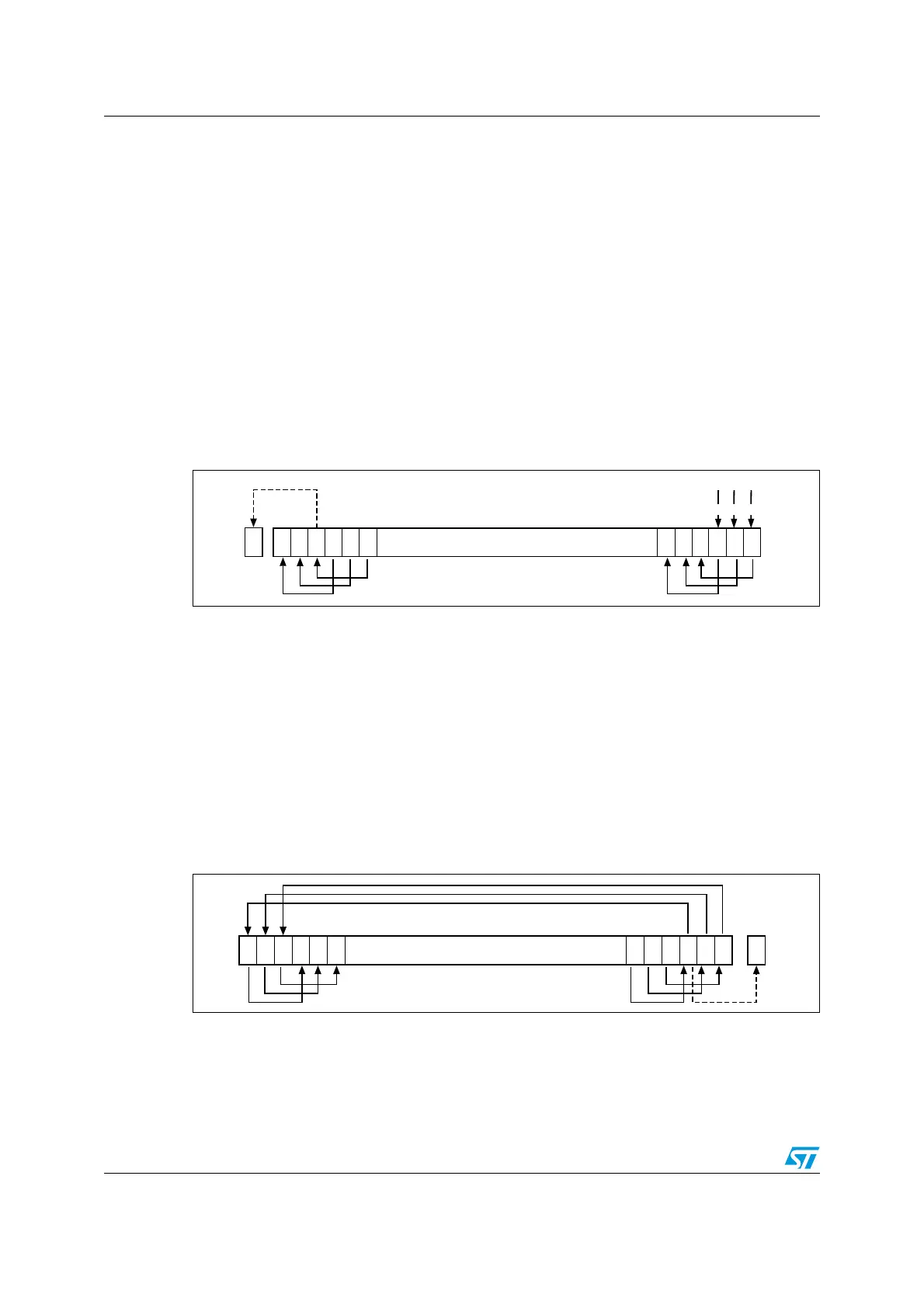

ROR

Rotate right by

n

bits moves the left-hand

32

-

n

bits of the register

Rm

, to the right by

n

places,

into the right-hand

32

-

n

bits of the result. It also moves the right-hand

n

bits of the register

into the left-hand

n

bits of the result (see Figure 13).

When the instruction is RORS, the carry flag is updated to the last bit rotation, bit[

n

-1], of the

register

Rm

.

Note: 1 If

n

is 32, then the value of the result is same as the value in

Rm

, and if the carry flag is

updated, it is updated to bit[31] of

Rm

.

2

ROR

with shift length,

n

, more than 32 is the same as

ROR

with shift length

n

-32.

Figure 13. ROR #3

Loading...

Loading...