PM0215 Core peripherals

Doc ID 022979 Rev 1 83/91

4.3.6 System handler priority registers (SHPRx)

The SHPR2-SHPR3 registers set the priority level, 0 to 192, of the exception handlers that

have configurable priority. SHPR2-SHPR3 are word accessible. To access the system

exception priority level using CMSIS, use the following CMSIS functions (where the input

parameter IRQn is the IRQ number):

● uint32_t NVIC_GetPriority(IRQn_Type IRQn)

● void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority)

Each PRI_n field is 8 bits wide, but the processor implements only bits[7:6] of each field,

and bits[5:0] read as zero and ignore writes.

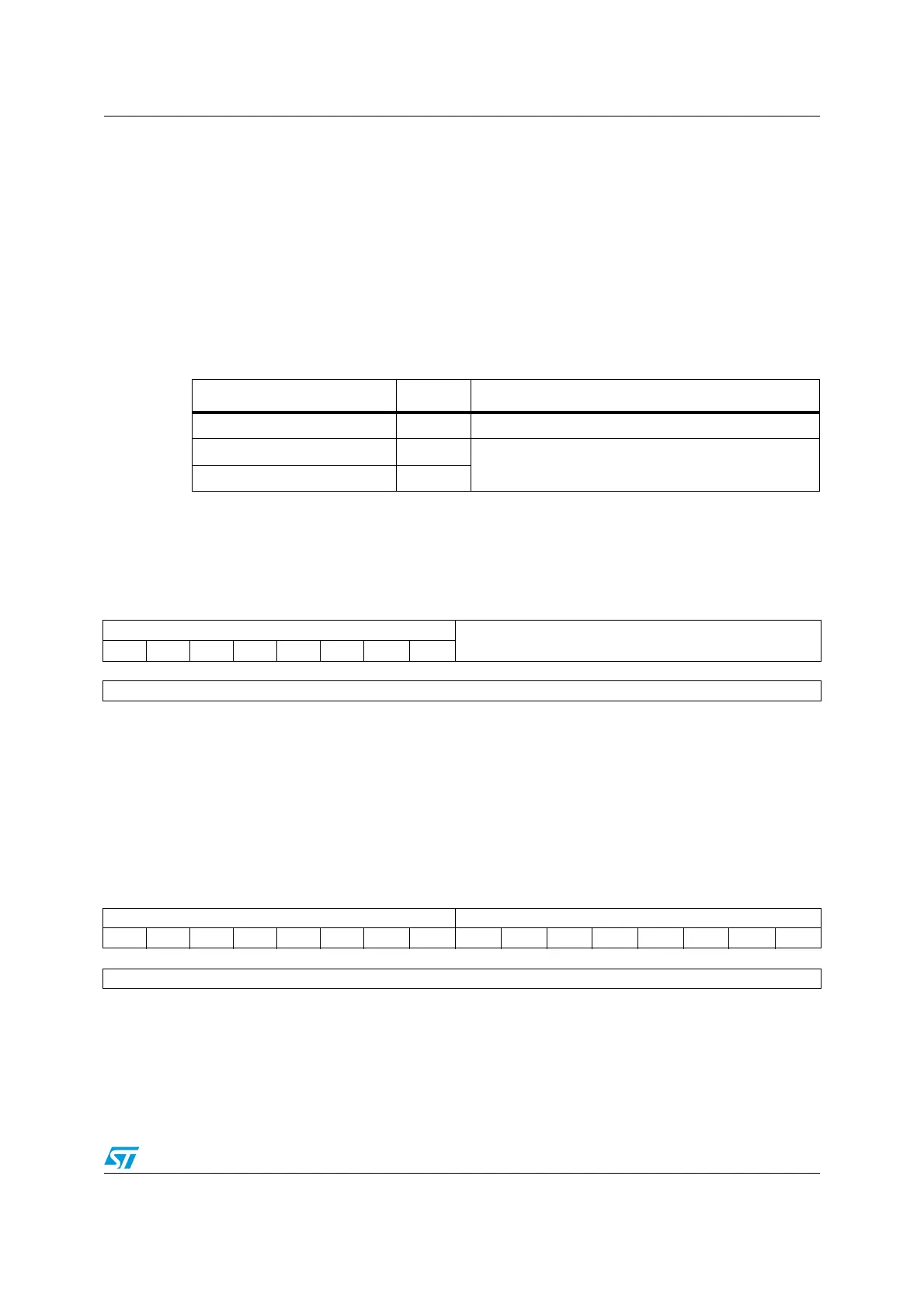

System handler priority register 2 (SHPR2)

Address offset: 0x1C

Reset value: 0x0000 0000

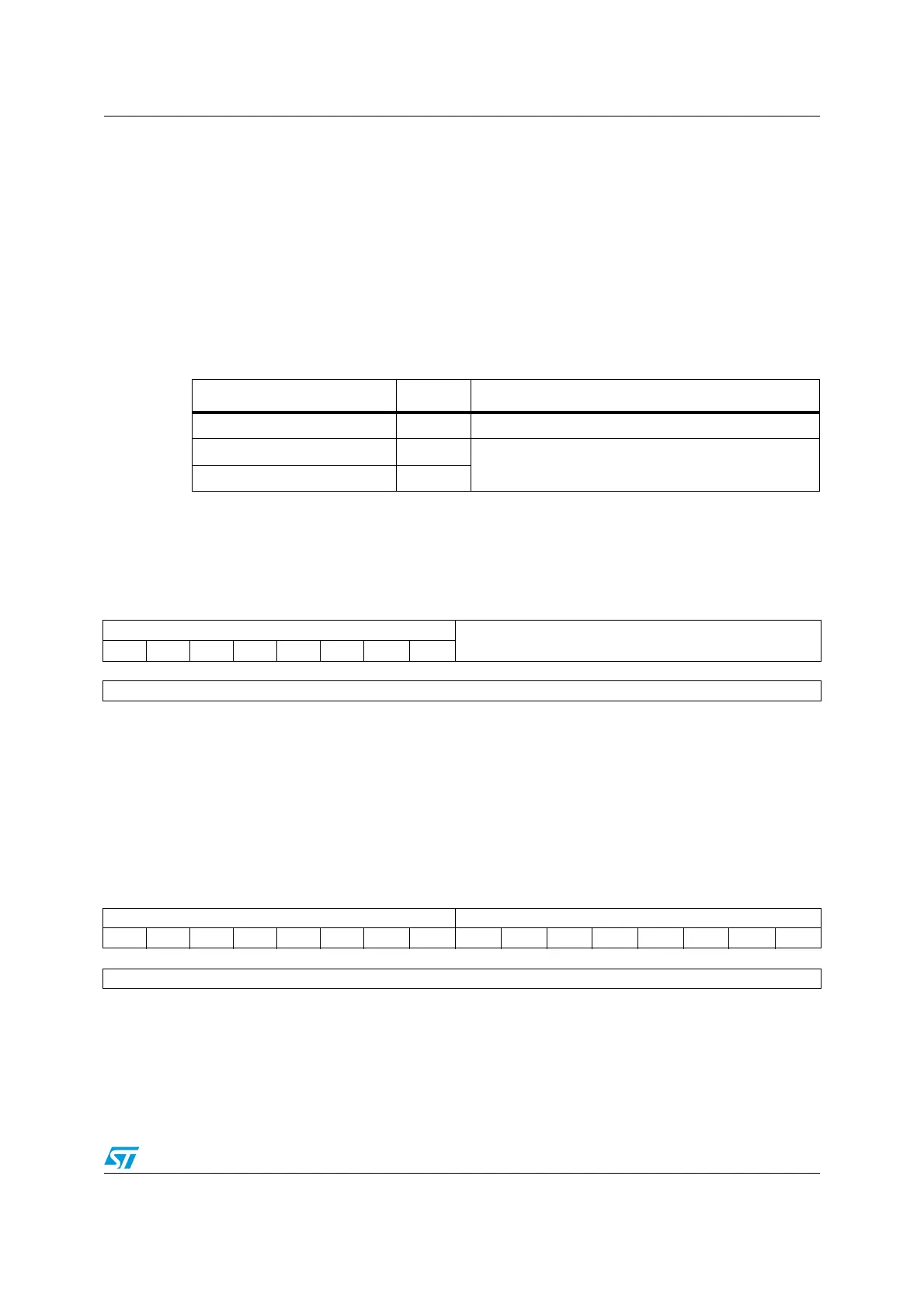

System handler priority register 3 (SHPR3)

Address: 0xE000 ED20

Reset value: 0x0000 0000

Table 31. System fault handler priority fields and registers

Handler Field Register description

SVCall PRI_11 System handler priority register 2 (SHPR2) on page 83

PendSV PRI_14

System handler priority register 3 (SHPR3) on page 83

SysTick PRI_15

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PRI_11

Reserved

rw rw rw rw r r r r

1514131211109876543210

Reserved

Bits 31:24 PRI_11: Priority of system handler 11, SVCall

Bits 23:0 Reserved, must be kept cleared

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PRI_15 PRI_14

rw rw rw rw r r r r rw rw rw rw r r r r

1514131211109876543210

Reserved

Bits 31:24 PRI_15: Priority of system handler 15, SysTick exception.

This is Reserved when the SysTick timer is not implemented.

Bits 23:16 PRI_14: Priority of system handler 14, PendSV

Bits 15:0 Reserved, must be kept cleared

Loading...

Loading...