Core peripherals PM0215

72/91 Doc ID 022979 Rev 1

4.2.4 Interrupt set-pending register (ISPR)

Address offset: 0x0100

Reset value: 0x0000 0000

This register forces interrupts into pending state, and shows which interrupts are pending.

4.2.5 Interrupt clear-pending register (ICPR)

Address offset: 0x0180

Reset value: 0x0000 0000

Removes pending state from interrupts and shows which interrupts are pending.

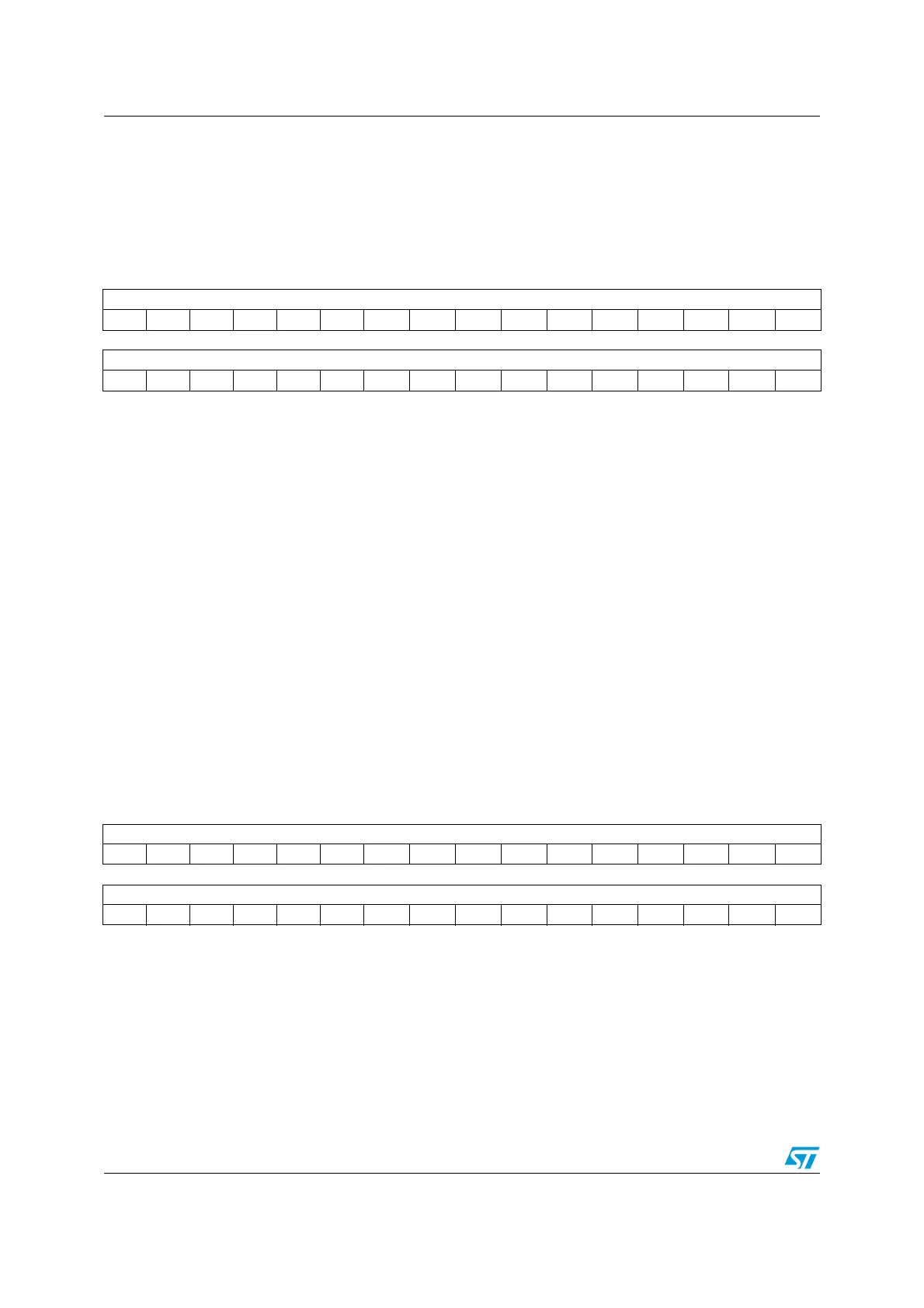

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

SETPEND[31:16]

rs rs rs rs rs rs rs rs rs rs rs rs rs rs rs rs

1514131211109876543210

SETPEND[15:0]

rs rs rs rs rs rs rs rs rs rs rs rs rs rs rs rs

Bits 31:0 SETPEND: Interrupt set-pending bits

Write:

0: No effect

1: Changes interrupt state to pending

Read:

0: Interrupt is not pending

1: Interrupt is pending

Writing 1 to the ISPR bit corresponding to an interrupt that is pending:

– has no effect.

Writing 1 to the ISPR bit corresponding to a disabled interrupt:

– sets the state of that interrupt to pending.

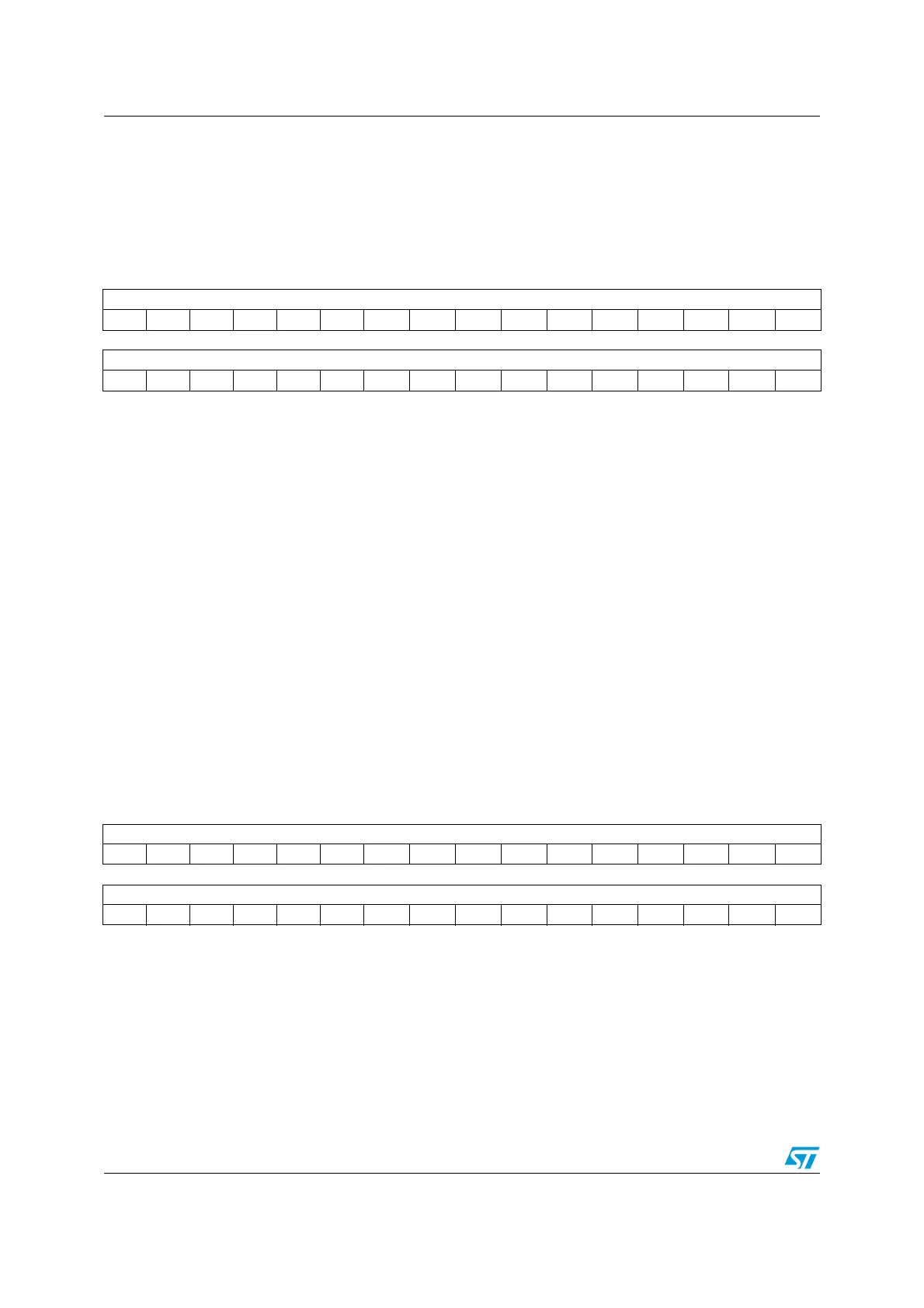

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

CLRPEND[31:16]

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1

1514131211109876543210

CLRPEND[15:0]

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1

Bits 31:0 CLRPEND: Interrupt clear-pending bits

Write:

0: No effect

1: Removes the pending state of an interrupt

Read:

0: Interrupt is not pending

1: Interrupt is pending

Writing 1 to an ICPR bit does not affect the active state of the corresponding interrupt.

Loading...

Loading...