PM0215 Core peripherals

Doc ID 022979 Rev 1 85/91

4.4 SysTick timer (STK)

When enabled, the timer:

● counts down from the reload value to zero,

● reloads (wraps to) the value in the STK_RVR on the next clock cycle,

● then decrements on subsequent clock cycles.

Writing a value of zero to the STK_RVR disables the counter on the next wrap.

When the counter transitions to zero, the COUNTFLAG status bit is set to 1.

Reading STK_CSR clears the COUNTFLAG bit to 0.

Writing to the STK_CVR clears the register and the COUNTFLAG status bit to 0. The write

does not trigger the SysTick exception logic.

Reading the register returns its value at the time it is accessed.

When the processor is halted for debugging the counter does not decrement.

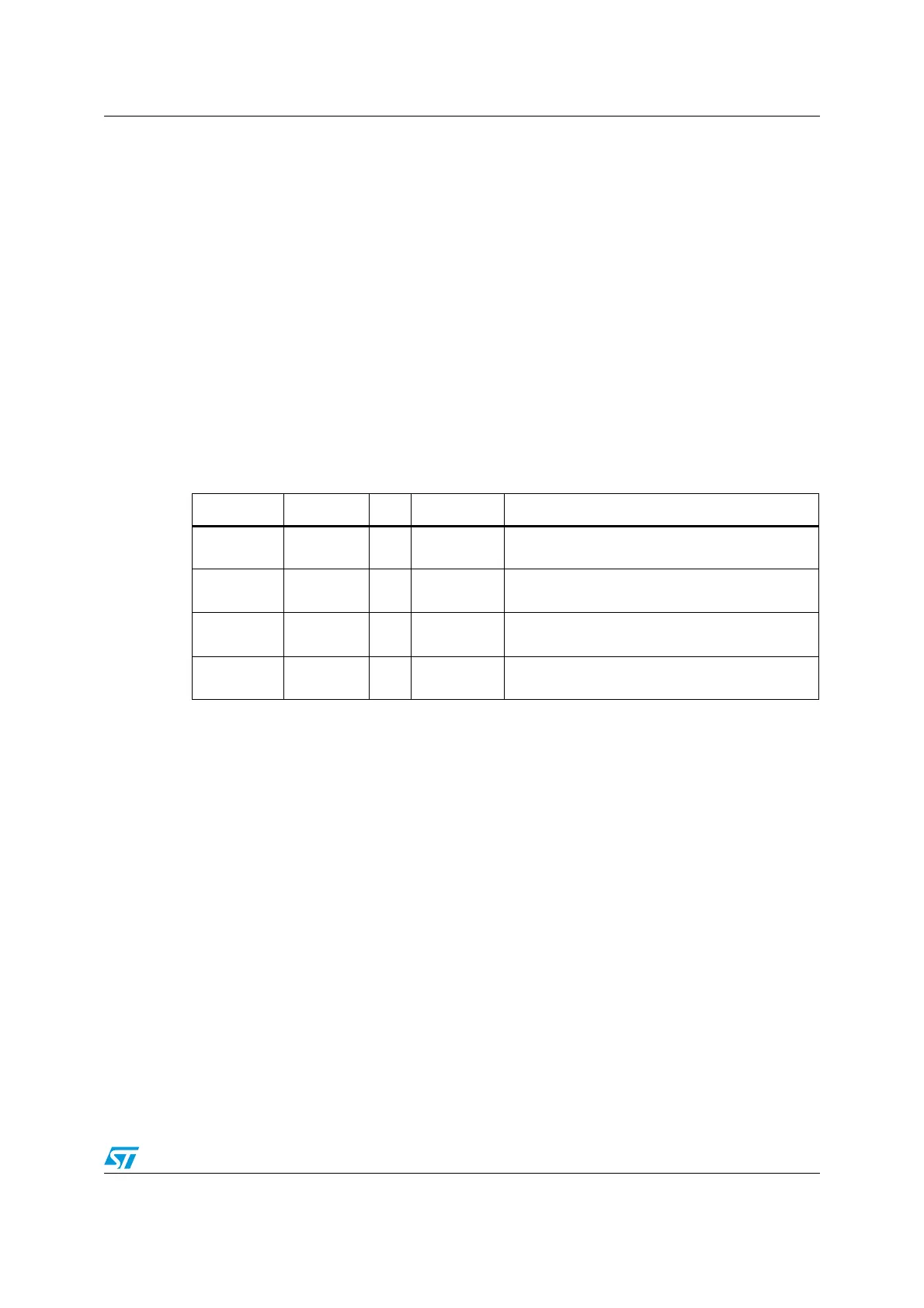

Table 33. System timer registers summary

Address Name Type Reset value Description

0xE000E010 STK_CSR RW 0x00000000

SysTick control and status register (STK_CSR)

on page 86

0xE000E014 STK_RVR RW Unknown

SysTick reload value register (STK_RVR) on

page 87

0xE000E018 STK_CVR RW Unknown

SysTick current value register (STK_CVR) on

page 87

0xE000E01C STK_CALIB RO 0xC0000000

SysTick calibration value register (STK_CALIB)

on page 88

Loading...

Loading...