PM0215 The STM32 Cortex-M0 instruction set

Doc ID 022979 Rev 1 35/91

3.2 CMSIS intrinsic functions

ISO/IEC C code cannot directly access some Cortex-M0 instructions. This section describes

intrinsic functions that can generate these instructions, provided by the CMIS and that might

be provided by a C compiler. If a C compiler does not support an appropriate intrinsic

function, you might have to use an inline assembler to access some instructions.

The CMSIS provides the intrinsic functions listed in Table 1 5 to generate instructions that

ISO/TEC C code cannot directly access.

The CMSIS also provides a number of functions for accessing the special registers using

MRS

and

MSR

instructions (see Ta bl e 16 ).

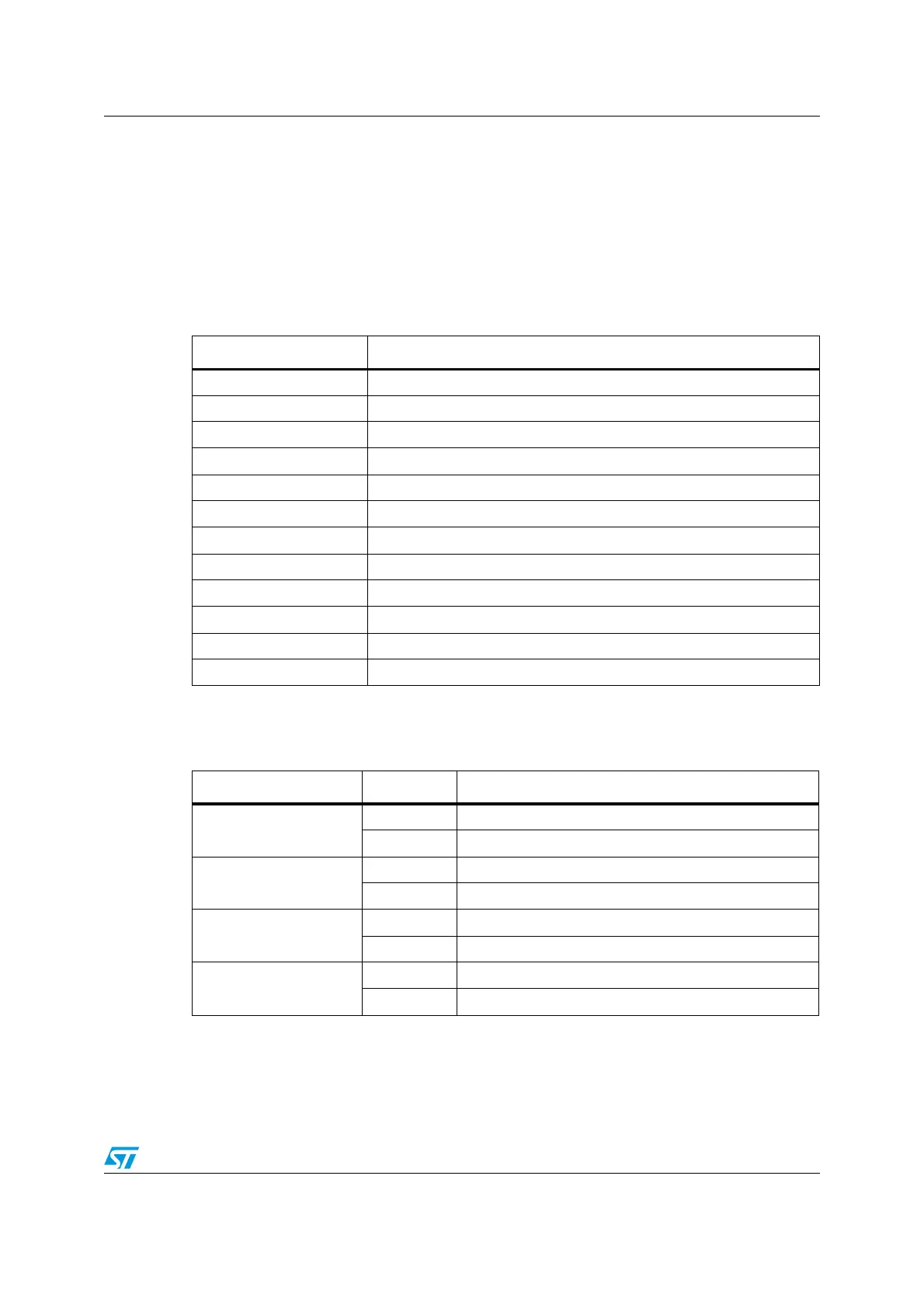

Table 15. CMSIS intrinsic functions to generate some Cortex-M0 instructions

Instruction CMSIS intrinsic function

CPSIE I void __enable_irq(void)

CPSID I void __disable_irq(void)

ISB void __ISB(void)

DSB void __DSB(void)

DMB void __DMB(void)

NOP void __NOP(void)

REV uint32_t __REV(uint32_t int value)

REV16 uint32_t __REV16(uint32_t int value)

REVSH uint32_t __REVSH(uint32_t int value)

SEV void __SEV(void)

WFE void __WFE(void)

WFI void __WFI(void)

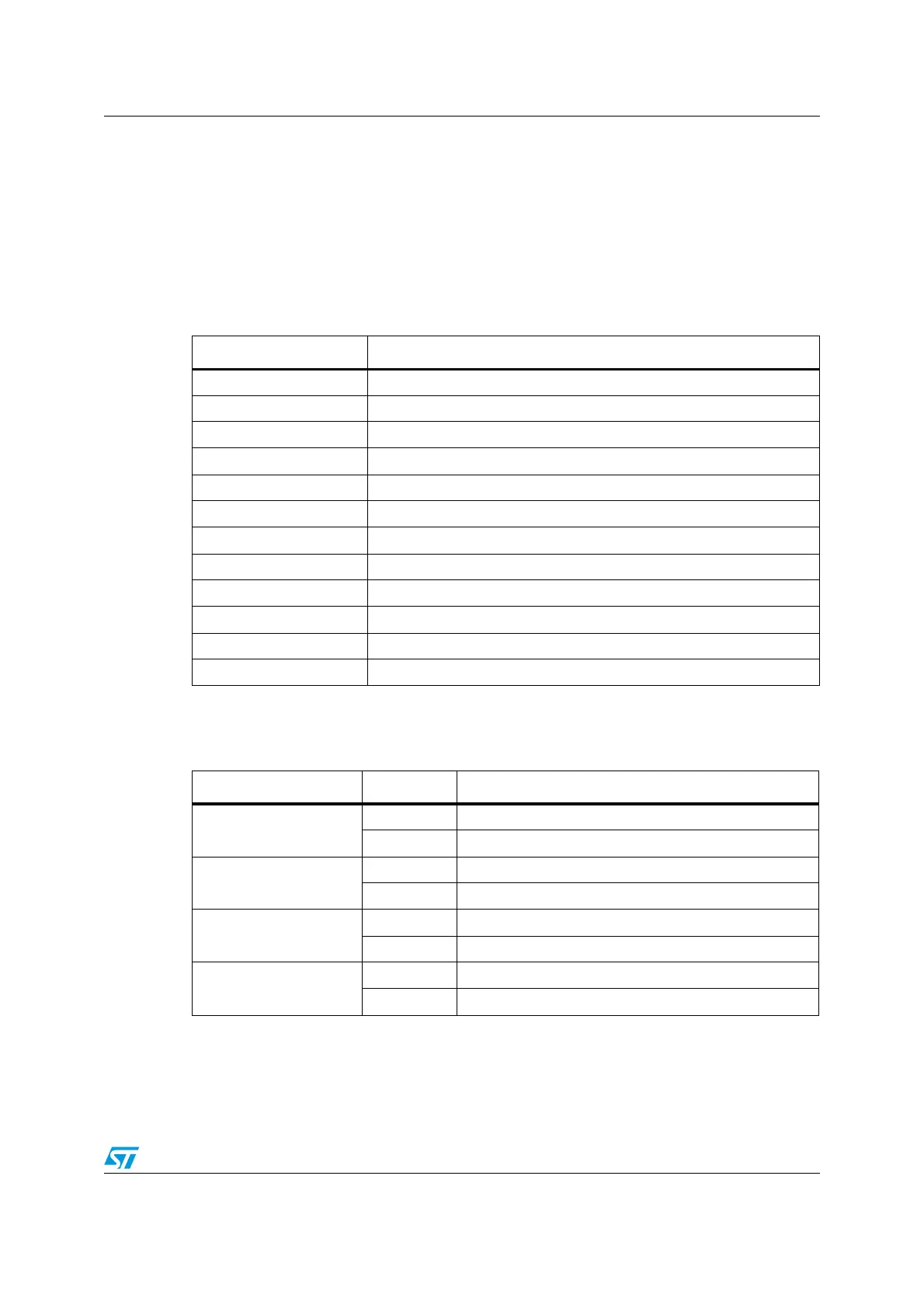

Table 16. CMSIS intrinsic functions to access the special registers

Special register Access CMSIS function

PRIMASK

Read uint32_t __get_PRIMASK (void)

Write void __set_PRIMASK (uint32_t value)

CONTROL

Read uint32_t __get_CONTROL (void)

Write void __set_CONTROL (uint32_t value)

MSP

Read uint32_t __get_MSP (void)

Write void __set_MSP (uint32_t TopOfMainStack)

PSP

Read uint32_t __get_PSP (void)

Write void __set_PSP (uint32_t TopOfProcStack)

Loading...

Loading...