The STM32 Cortex-M0 instruction set PM0215

34/91 Doc ID 022979 Rev 1

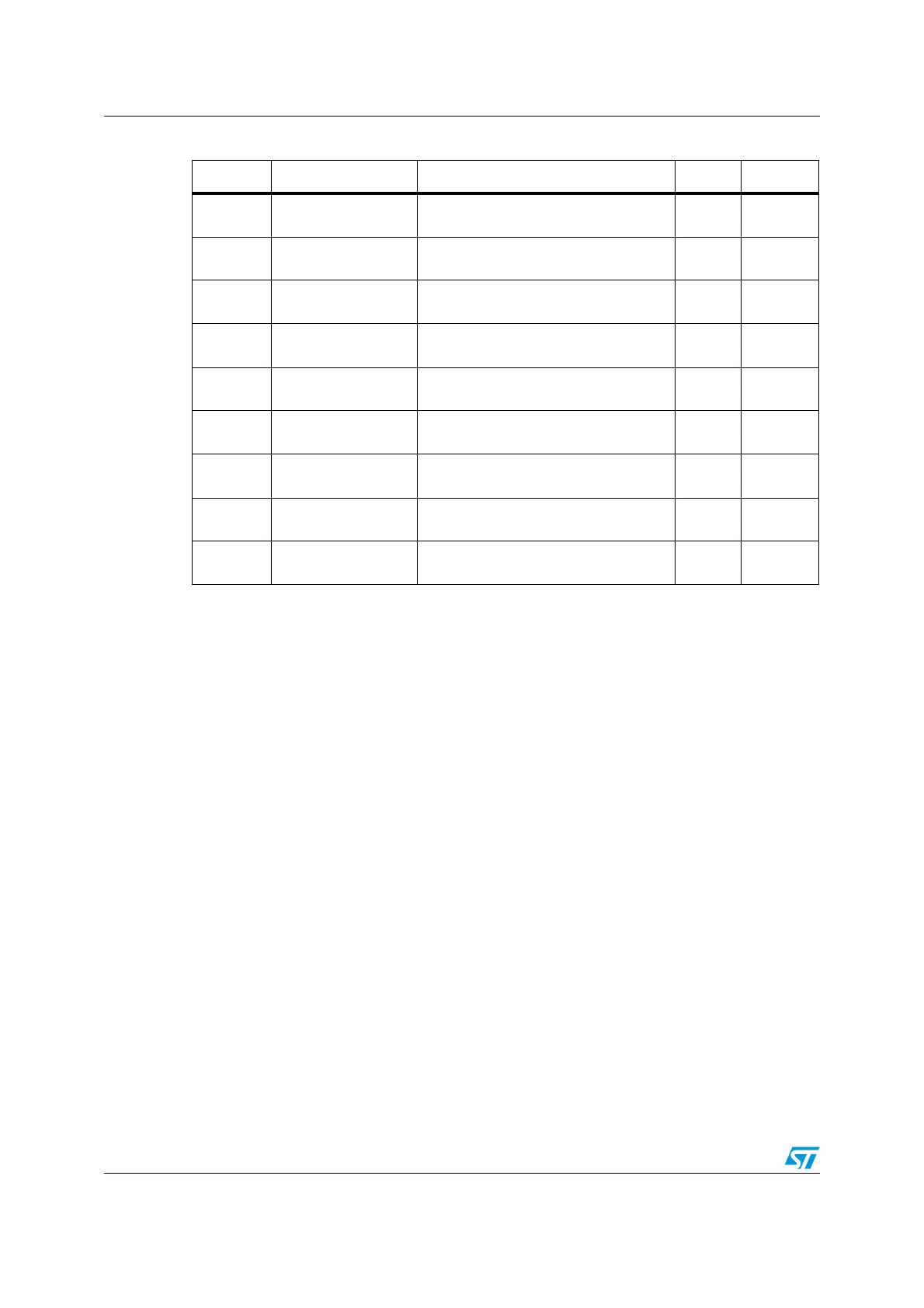

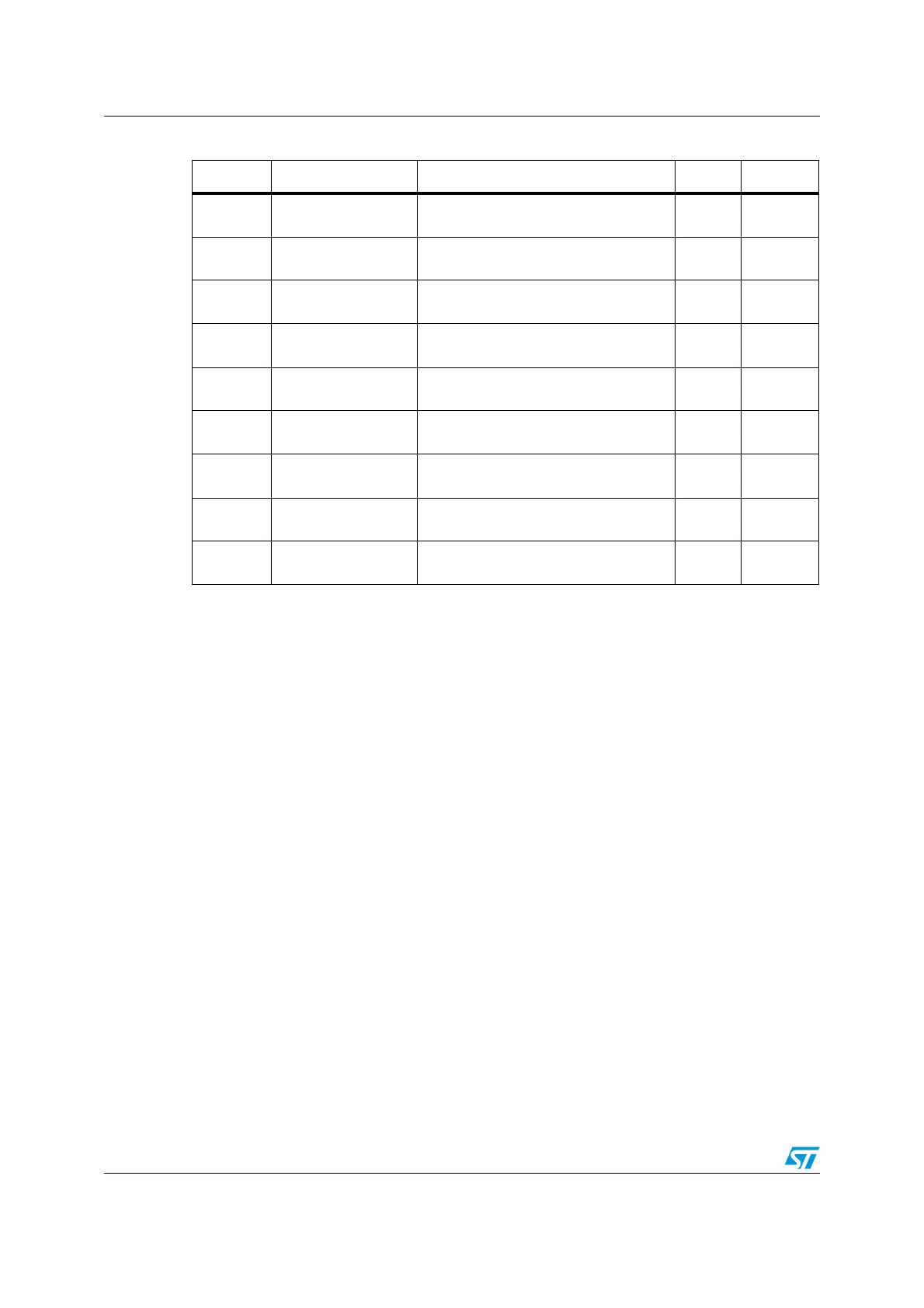

SUB{S} {Rd,} Rn, <Rm|#imm> Subtract N,Z,C,V

3.5.1 on

page 49

SVC #imm Supervisor call -

3.7.10 on

page 67

SXTB Rd, Rm Sign extend byte -

3.5.8 on

page 57

SXTH Rd, Rm Sign extend halfword -

3.5.8 on

page 57

TST Rn, Rm Logical AND based test N,Z

3.5.9 on

page 58

UXTB Rd, Rm Zero extend a byte -

3.5.8 on

page 57

UXTH Rd, Rm Zero extend a halfword -

3.5.8 on

page 57

WFE - Wait for event -

3.7.11 on

page 67

WFI - Wait for interrupt -

3.7.12 on

page 68

Table 14. Cortex-M0 instructions

Mnemonic Operands Brief description Flags Page

Loading...

Loading...