PM0215 The STM32 Cortex-M0 instruction set

Doc ID 022979 Rev 1 33/91

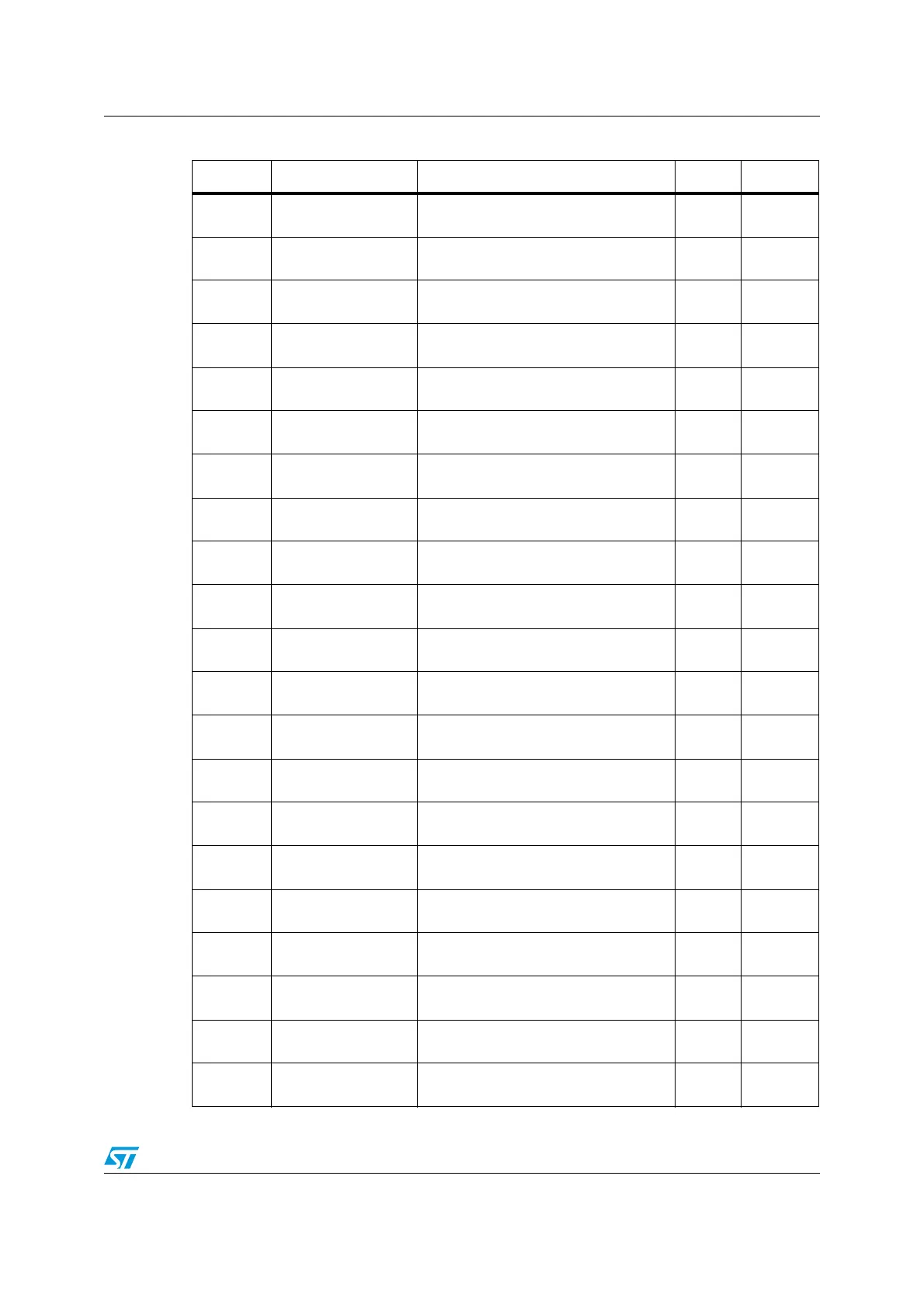

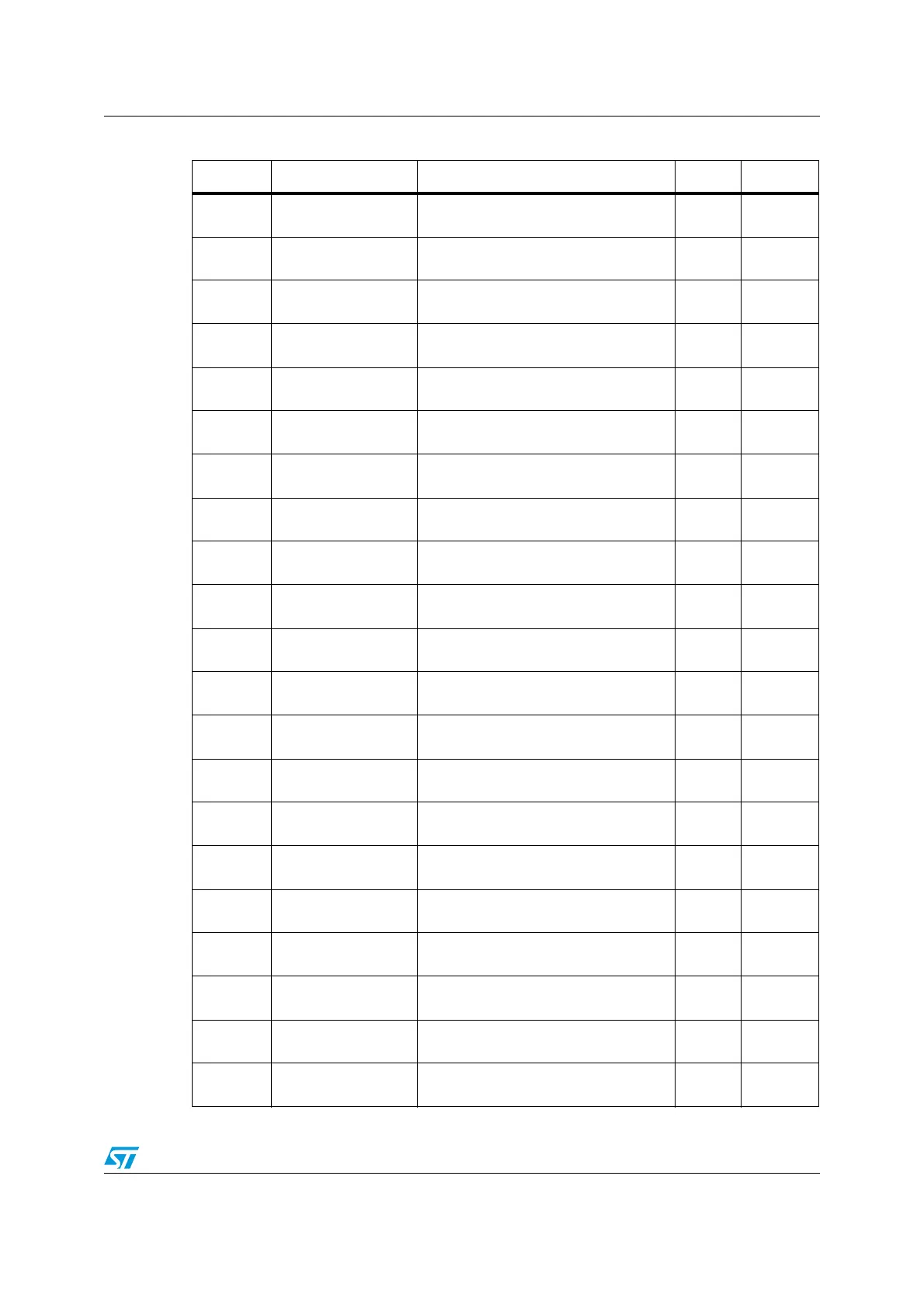

LSRS {Rd,} Rn, <Rs|#imm> Logical shift right N,Z,C

3.5.3 on

page 52

MOV{S} Rd, Rm Move N,Z

3.5.5 on

page 54

MRS Rd, spec_reg

Move to general register from special

register

-

3.7.6 on

page 64

MSR spec_reg, Rm

Move to special register from general

register

N,Z,C,V

3.7.7 on

page 65

MULS Rd,

Rn, Rm Multiply, 32-bit result N,Z

3.5.6 on

page 55

MVNS Rd, Rm Bitwise NOT N,Z

3.5.5 on

page 54

NOP - No operation -

3.7.8 on

page 66

ORRS {Rd,}

Rn, Rm Logical OR N,Z

3.5.2 on

page 51

POP reglist Pop registers from stack -

3.4.6 on

page 47

PUSH reglist Push registers onto stack -

3.4.6 on

page 47

REV Rd, Rm Byte-reverse word -

3.5.7 on

page 56

REV16 Rd, Rm Byte-reverse packed halfwords -

3.5.7 on

page 56

REVSH Rd, Rm Byte-reverse signed halfword -

3.5.7 on

page 56

RORS {Rd,}

Rn, Rs Rotate right N,Z,C

3.5.3 on

page 52

RSBS {Rd,}

Rn, #0 Reverse subtract N,Z,C,V

3.5.1 on

page 49

SBCS {Rd,}

Rn, Rm Subtract with carry N,Z,C,V

3.5.1 on

page 49

SEV - Send event -

3.7.9 on

page 66

STM Rn!, reglist Store multiple registers, increment after -

3.4.5 on

page 46

STR Rt, [Rn, <Rm|#imm>] Store register as word -

3.4.2 on

page 43

STRB Rt, [Rn, <Rm|#imm>] Store register as byte -

3.4.2 on

page 43

STRH Rt, [Rn, <Rm|#imm>] Store register as halfword -

3.4.2 on

page 43

Table 14. Cortex-M0 instructions

Mnemonic Operands Brief description Flags Page

Loading...

Loading...