Core peripherals PM0215

82/91 Doc ID 022979 Rev 1

4.3.5 Configuration and control register (CCR)

Address offset: 0x14

Reset value: 0x0000 0204

The CCR is a read-only register and indicates some aspects of the behavior of the Cortex-

M0 processor.

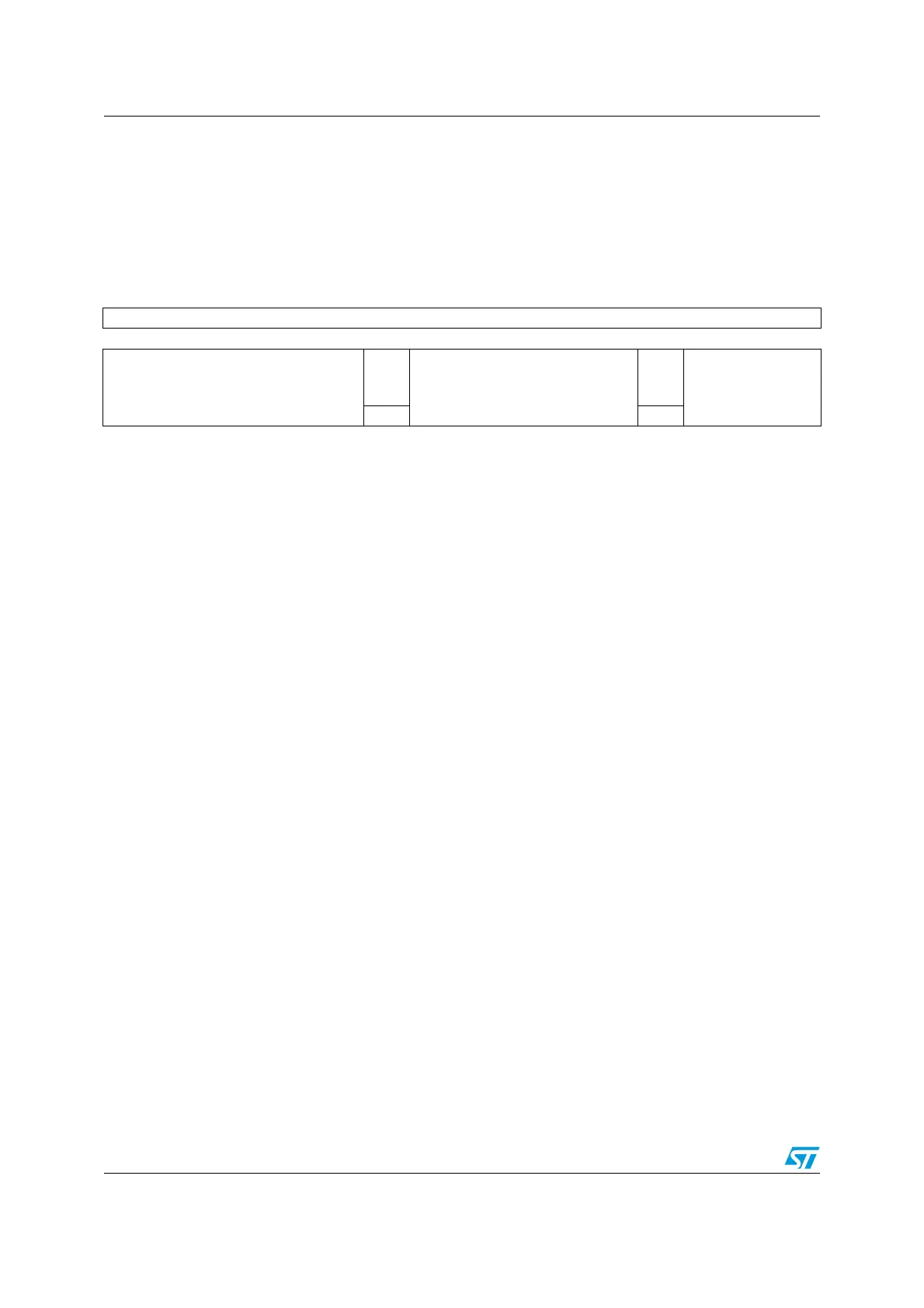

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

STK

ALIGN

Reserved

UN

ALIGN_

TRP

Reserved

rw rw

Bits 31:10 Reserved, must be kept cleared

Bit 9 STKALIGN

Always reads as one, indicates 8-byte stack alignment on exception entry.

On exception entry, the processor uses bit[9] of the stacked PSR to indicate the stack

alignment. On return from the exception it uses this stacked bit to restore the correct stack

alignment.

Bits 8:4 Reserved, must be kept cleared

Bit 3 UNALIGN_ TRP

Always reads as one, indicates that all unaligned accesses generate a HardFault.

Bits 2:0 Reserved, must be kept cleared

Loading...

Loading...