PM0215 The STM32 Cortex-M0 instruction set

Doc ID 022979 Rev 1 31/91

3 The STM32 Cortex-M0 instruction set

This chapter is the reference material for the Cortex-M0 instruction set description in a User

Guide. The following sections give general information:

Section 3.1: Instruction set summary on page 31

Section 3.2: CMSIS intrinsic functions on page 35

Section 3.3: About the instruction descriptions on page 36

Each of the following sections describes a functional group of Cortex-M0 instructions.

Together they describe all the instructions supported by the Cortex-M0 processor:

Section 3.4: Memory access instructions on page 41

Section 3.5: General data processing instructions on page 48

Section 3.6: Branch and control instructions on page 59

Section 3.7: Miscellaneous instructions on page 61

3.1 Instruction set summary

The processor implements a version of the thumb instruction set. Ta bl e 1 4 lists the

supported instructions.

In Ta b le 14 :

● Angle brackets, <>, enclose alternative forms of the operand

● Braces, {}, enclose optional operands

● The operands column is not exhaustive

● Op2 is a flexible second operand that can be either a register or a constant

● Most instructions can use an optional condition code suffix

For more information on the instructions and operands, see the instruction descriptions.

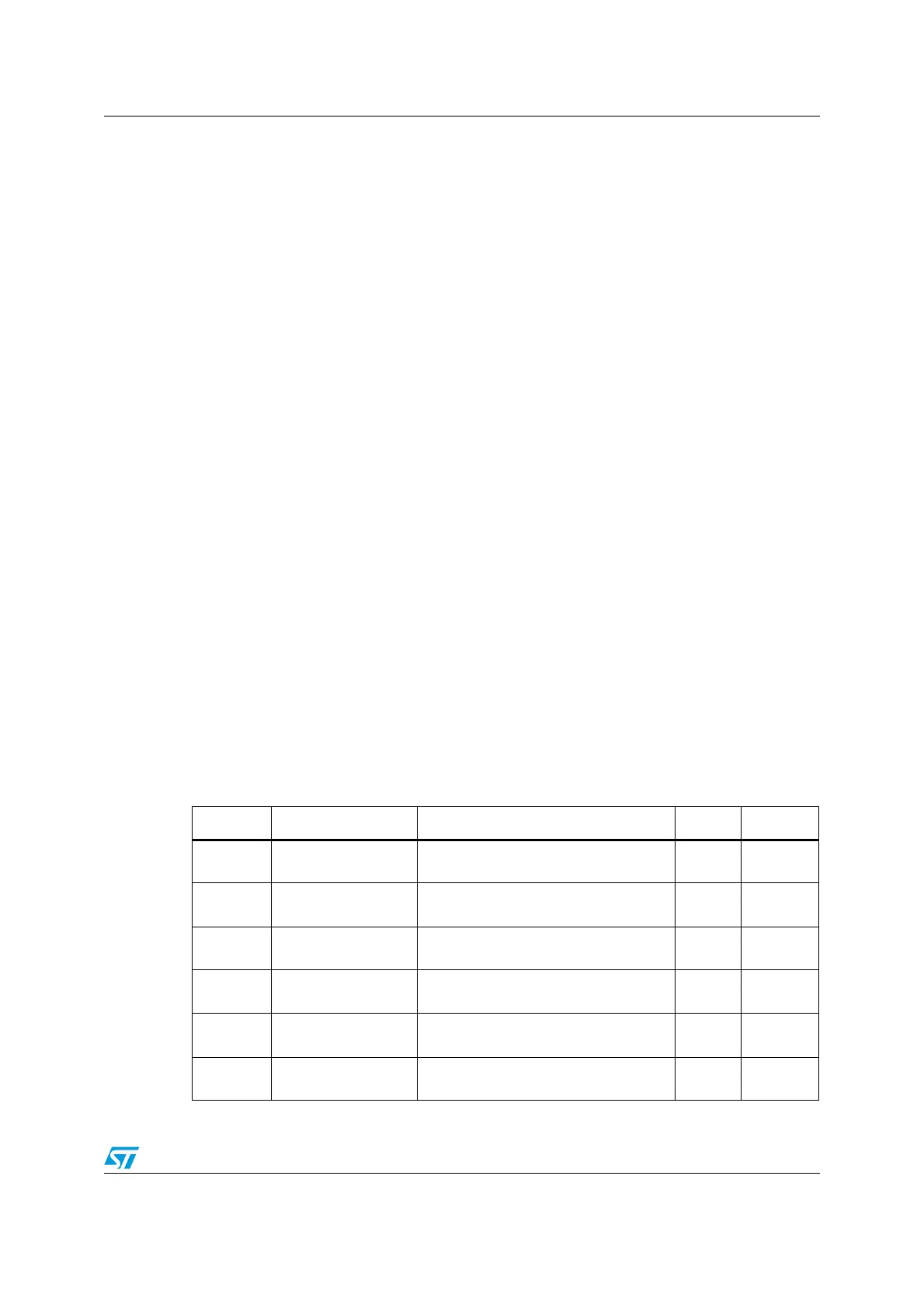

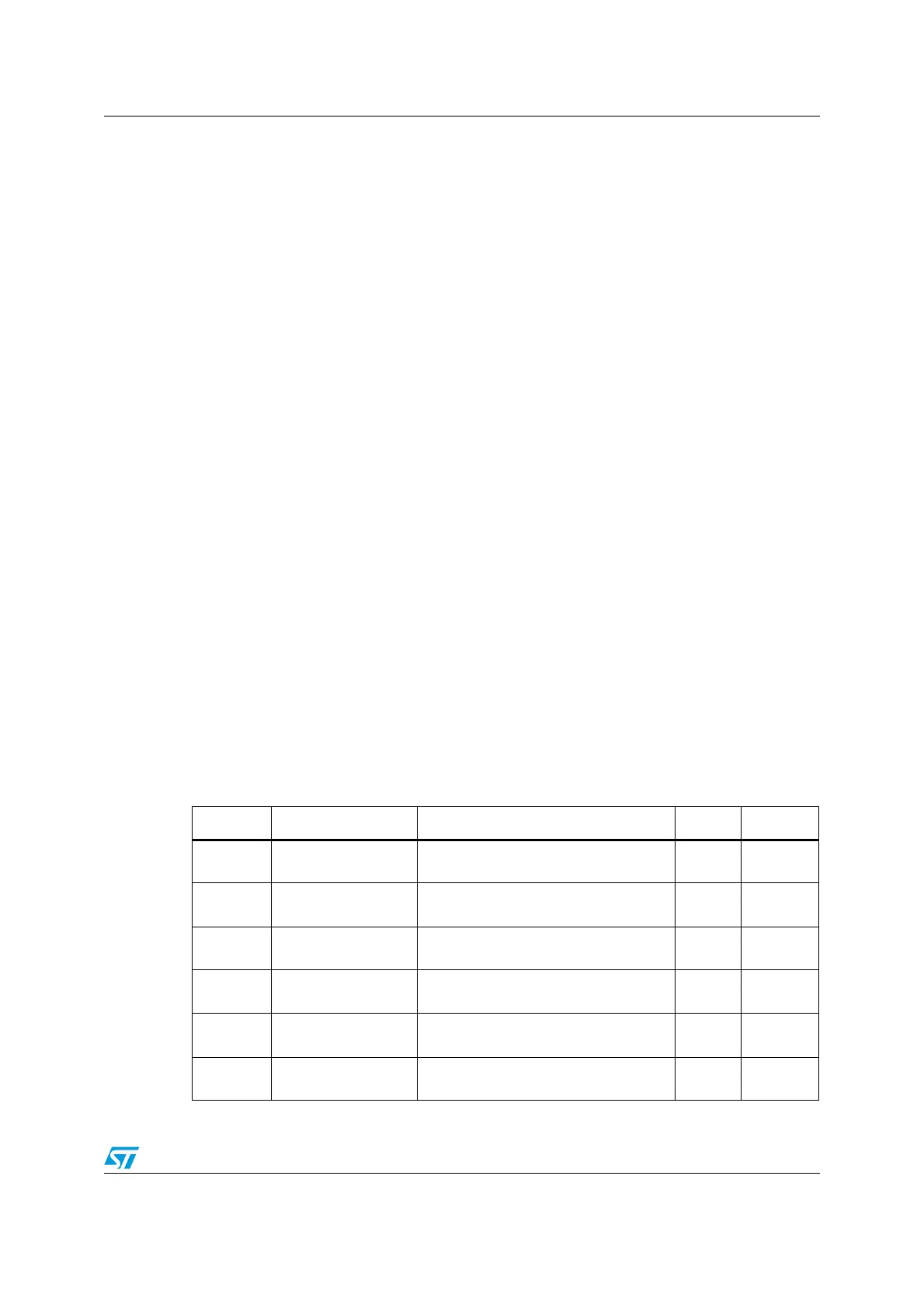

Table 14. Cortex-M0 instructions

Mnemonic Operands Brief description Flags Page

ADCS {Rd,}

Rn, Rm Add with carry N,Z,C,V

3.5.1 on

page 49

ADD{S} {Rd,}

Rn, <Rm|#imm> Add N,Z,C,V

3.5.1 on

page 49

ADR Rd, label PC-relative address to register -

3.4.1 on

page 42

ANDS {Rd,}

Rn, Rm Bitwise AND N,Z

3.5.2 on

page 51

ASRS {Rd,} Rm, <Rs|#imm> Arithmetic shift right N,Z,C

3.5.3 on

page 52

B{cc} label Branch {conditionally} -

3.6.1 on

page 59

Loading...

Loading...