Core peripherals PM0215

86/91 Doc ID 022979 Rev 1

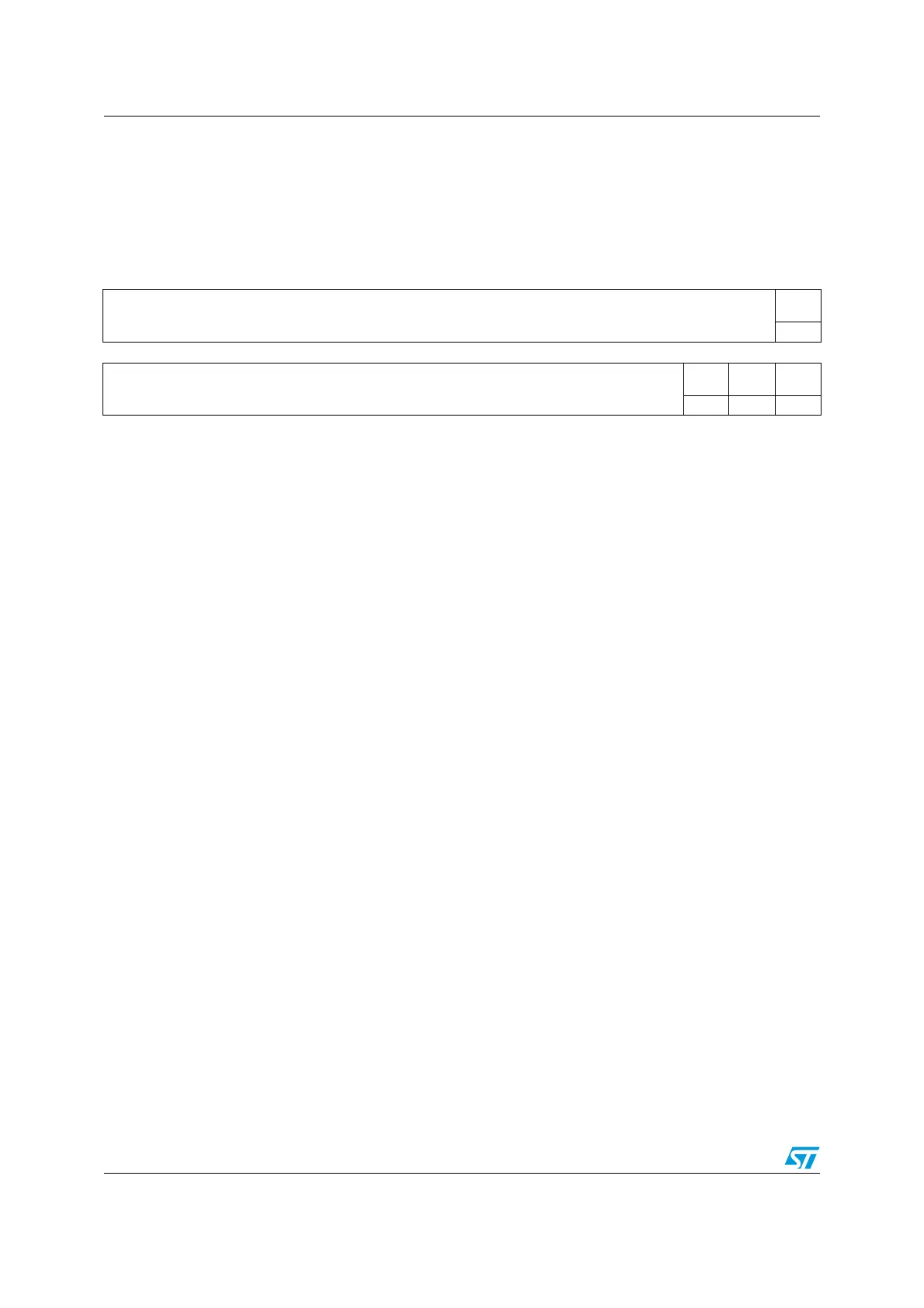

4.4.1 SysTick control and status register (STK_CSR)

Address offset: 0x00

Reset value: 0x0000 0004

The SysTick CSR register enables the SysTick features.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

COUNT

FLAG

rw

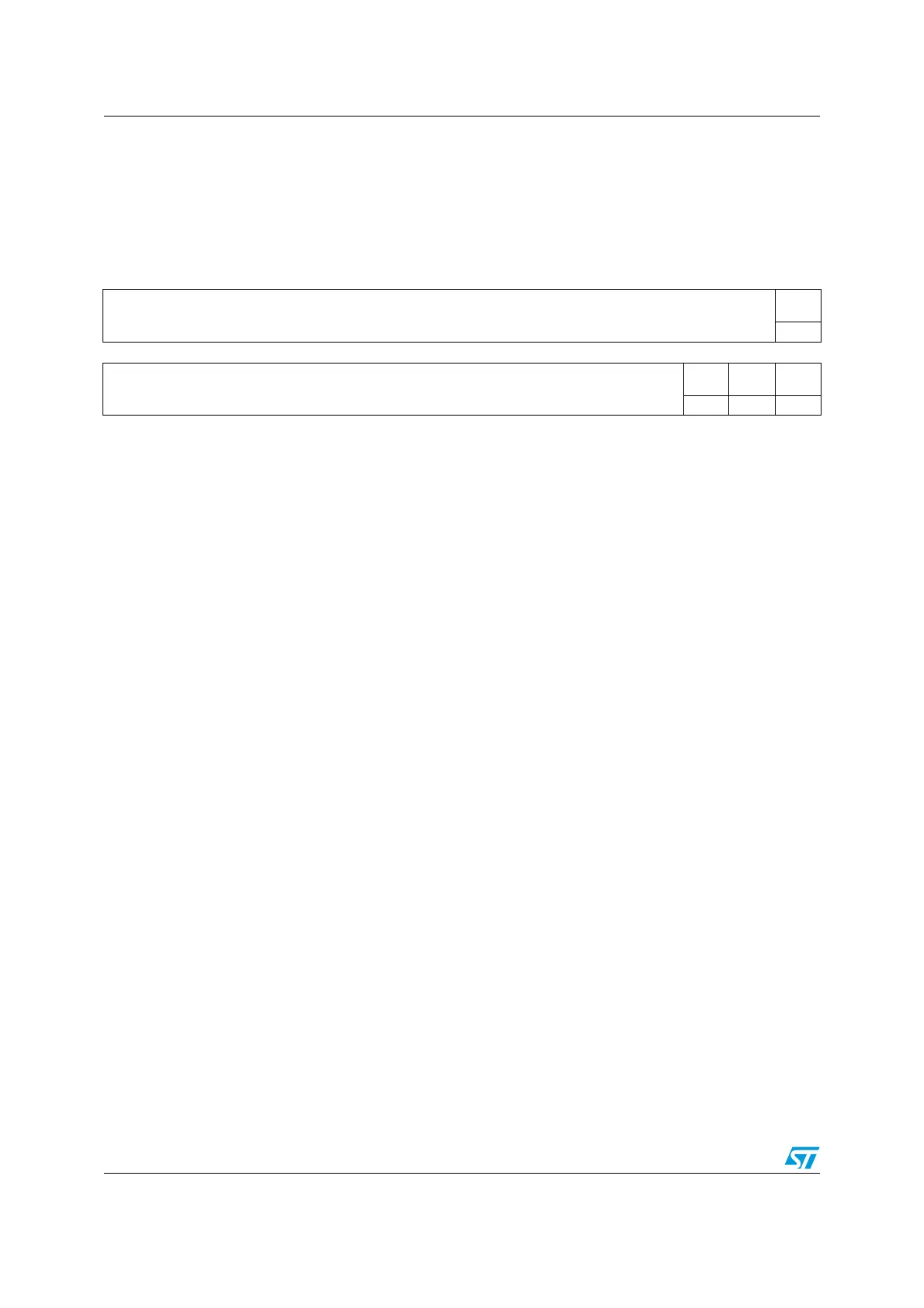

1514131211109876543210

Reserved

CLKSO

URCE

TICK

INT

EN

ABLE

rw rw rw

Bits 31:17 Reserved, must be kept cleared.

Bit 16 COUNTFLAG:

Returns 1 if timer counted to 0 since last time this was read.

Bits 15:3 Reserved, must be kept cleared.

Bit 2 CLKSOURCE: Clock source selection

Selects the timer clock source.

0: External reference clock

1: Processor clock

Bit 1 TICKINT: SysTick exception request enable

0: Counting down to zero does not assert the SysTick exception request

1: Counting down to zero to asserts the SysTick exception request.

Bit 0 ENABLE: Counter enable

Enables the counter. When ENABLE is set to 1, the counter starts counting down. On reaching

0, it sets the COUNTFLAG to 1 and optionally asserts the SysTick depending on the value of

TICKINT. It then loads the RELOAD value again, and begins counting.

0: Counter disabled

1: Counter enabled

Loading...

Loading...