Core peripherals PM0215

70/91 Doc ID 022979 Rev 1

4.2 Nested vectored interrupt controller (NVIC)

This section describes the Nested Vectored Interrupt Controller (NVIC) and the registers it

uses. The NVIC supports:

● Up to 32 interrupts

● A programmable priority level of 0-192 in steps of 64 for each interrupt. A higher level

corresponds to a lower priority, so level 0 is the highest interrupt priority

● Level and pulse detection of interrupt signals

● Interrupt tail-chaining

● An external Non-maskable interrupt (NMI)

The processor automatically stacks its state on exception entry and unstacks this state on

exception exit, with no instruction overhead. This provides low latency exception handling.

The hardware implementation of the NVIC registers is:

4.2.1 Accessing the Cortex-M0 NVIC registers using CMSIS

CMSIS functions enable software portability between different Cortex-M profile processors.

To access the NVIC registers when using CMSIS, use the following functions:

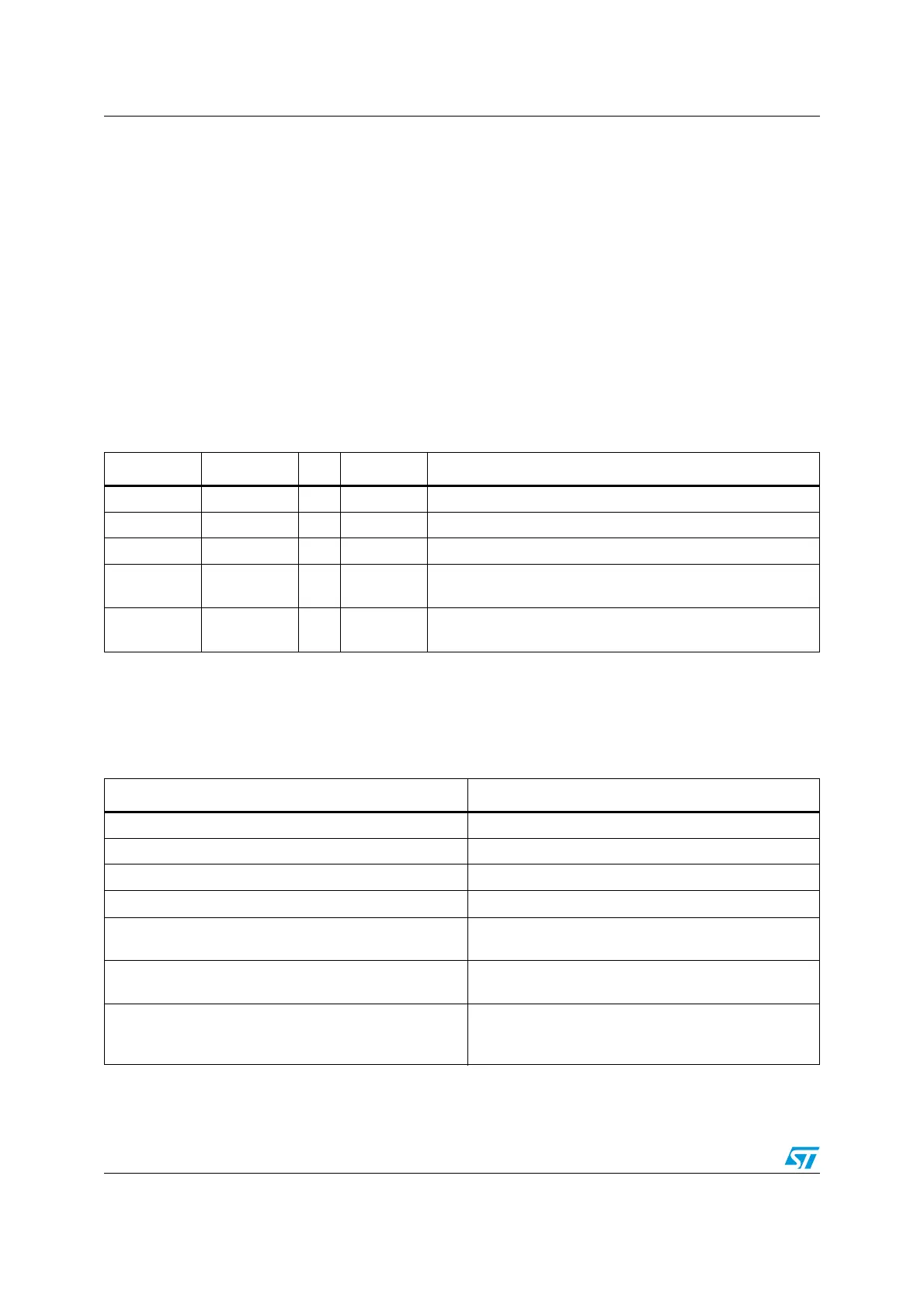

Table 25. NVIC register summary

Address Name Type Reset value Description

0xE000E100 ISER RW 0x00000000 Table 4.2.2: Interrupt set-enable register (ISER) on page 71

0XE000E180 ICER RW 0x00000000 Table 4.2.3: Interrupt clear-enable register (ICER) on page 71

0XE000E200 ISPR RW 0x00000000 Table 4.2.4: Interrupt set-pending register (ISPR) on page 72

0XE000E280 ICPR RW 0x00000000

Table 4.2.5: Interrupt clear-pending register (ICPR) on

page 72

0xE000E400-

0xE000E41C

IPR0-IPR7 RW 0x00000000 Table 4.2.6: Interrupt priority register (IPR0-IPR7) on page 73

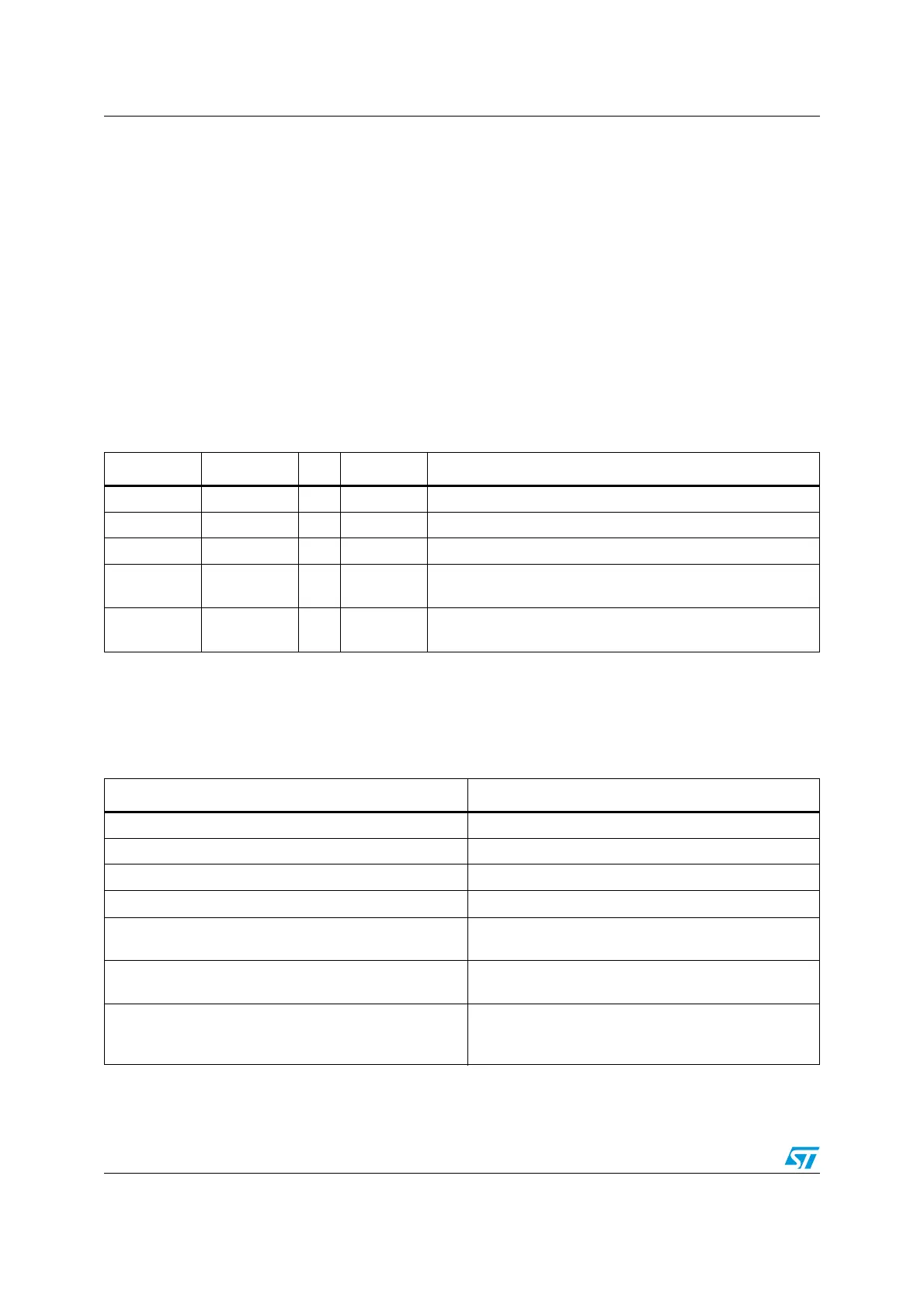

Table 26. CMSIS access NVIC functions

CMSIS function

(1)

Description

void NVIC_EnableIRQ(IRQn_Type IRQn) Enables an interrupt or exception.

void NVIC_DisableIRQ(IRQn_Type IRQn) Disables an interrupt or exception.

void NVIC_SetPendingIRQ(IRQn_Type IRQn) Sets pending status of interrupt or exception to 1.

void NVIC_ClearPendingIRQ(IRQn_Type IRQn) Clears pending status of interrupt / exception to 0.

uint32_t NVIC_GetPendingIRQ(IRQn_Type IRQn)

Reads the pending status of interrupt / exception.

Returns non-zero value if pending status is set to 1.

void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority)

Sets priority of an interrupt / exception with configurable

priority level to 1.

uint32_t NVIC_GetPriority(IRQn_Type IRQn)

Reads priority of an interrupt or exception with

configurable priority level.

Returns the current priority level.

1. The input parameter IRQn is the IRQ number,

Loading...

Loading...