PM0215 Core peripherals

Doc ID 022979 Rev 1 77/91

4.3 System control block (SCB)

The System control block (SCB) provides system implementation information, and system

control. This includes configuration, control, and reporting of the system exceptions. To

improve software efficiency, the CMSIS simplifies the SCB register presentation, in the

CMSIS, the array SHP[1] corresponds to the registers SHPR2-SHPR3.

4.3.1 CPUID base register (CPUID)

Address offset: 0x00

Reset value: 0x410C C200

The CPUID register contains the processor part number, version, and implementation

information.

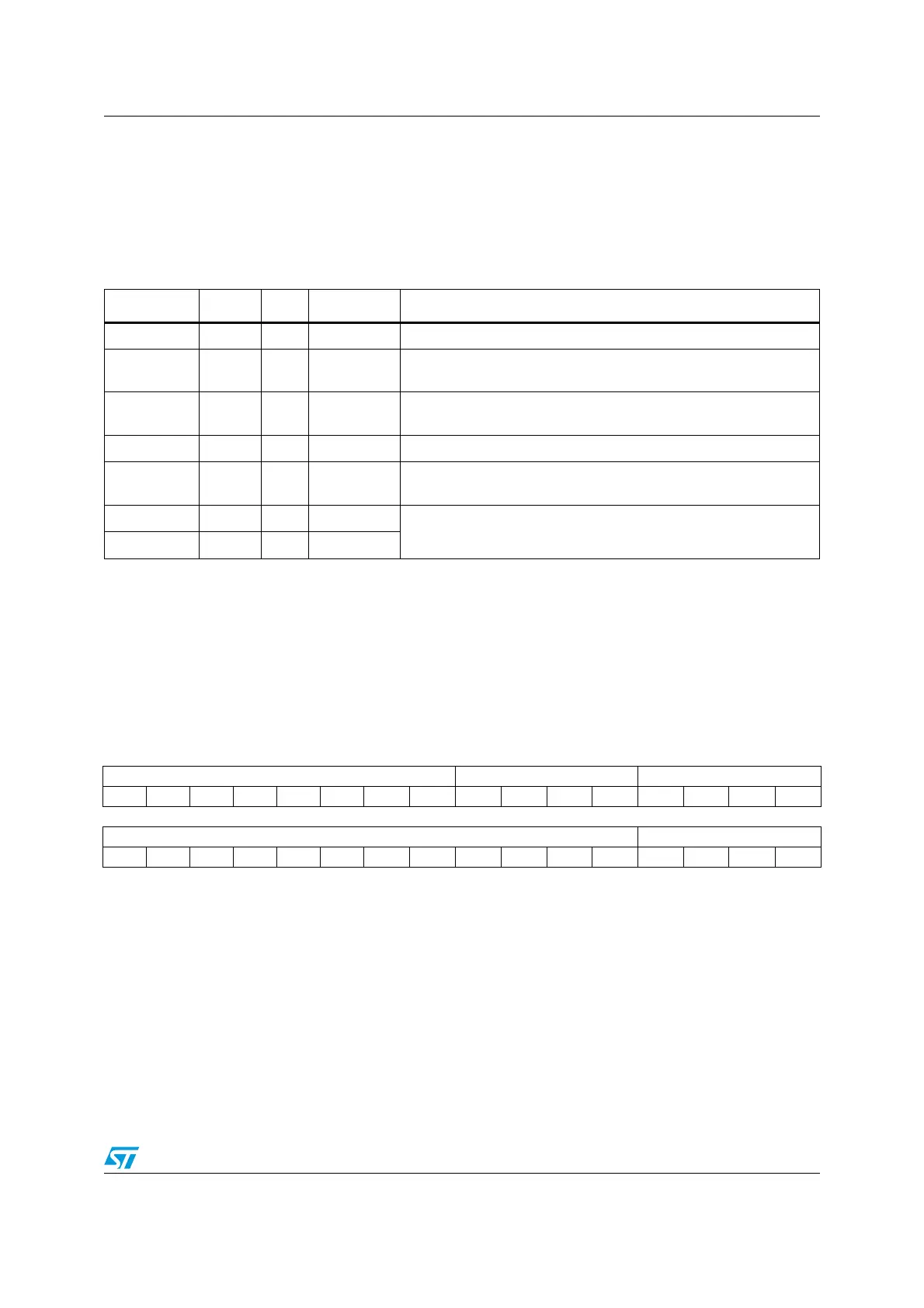

Table 30. Summary of the system control block registers

Address Name Type Reset value Description

0xE000ED00 CPUID RO 0x410CC200 Section 4.3.1: CPUID base register (CPUID) on page 77

0xE000ED04 ICSR RW

(1)

0x00000000

Section 4.3.2: Interrupt control and state register (ICSR) on

page 78

0xE000ED0C AIRCR RW

(1)

0xFA050000

Section 4.3.3: Application interrupt and reset control register

(AIRCR) on page 80

0xE000ED10 SCR RW 0x00000000 Section 4.3.4: System control register (SCR) on page 81

0xE000ED14 CCR RW 0x00000204

Section 4.3.5: Configuration and control register (CCR) on

page 82

0xE000ED1C SHPR2 RW 0x00000000

Section 4.3.6: System handler priority registers (SHPRx) on

page 83

0xE000ED20 SHPR3 RW 0x00000000

1. See the register description for more information.

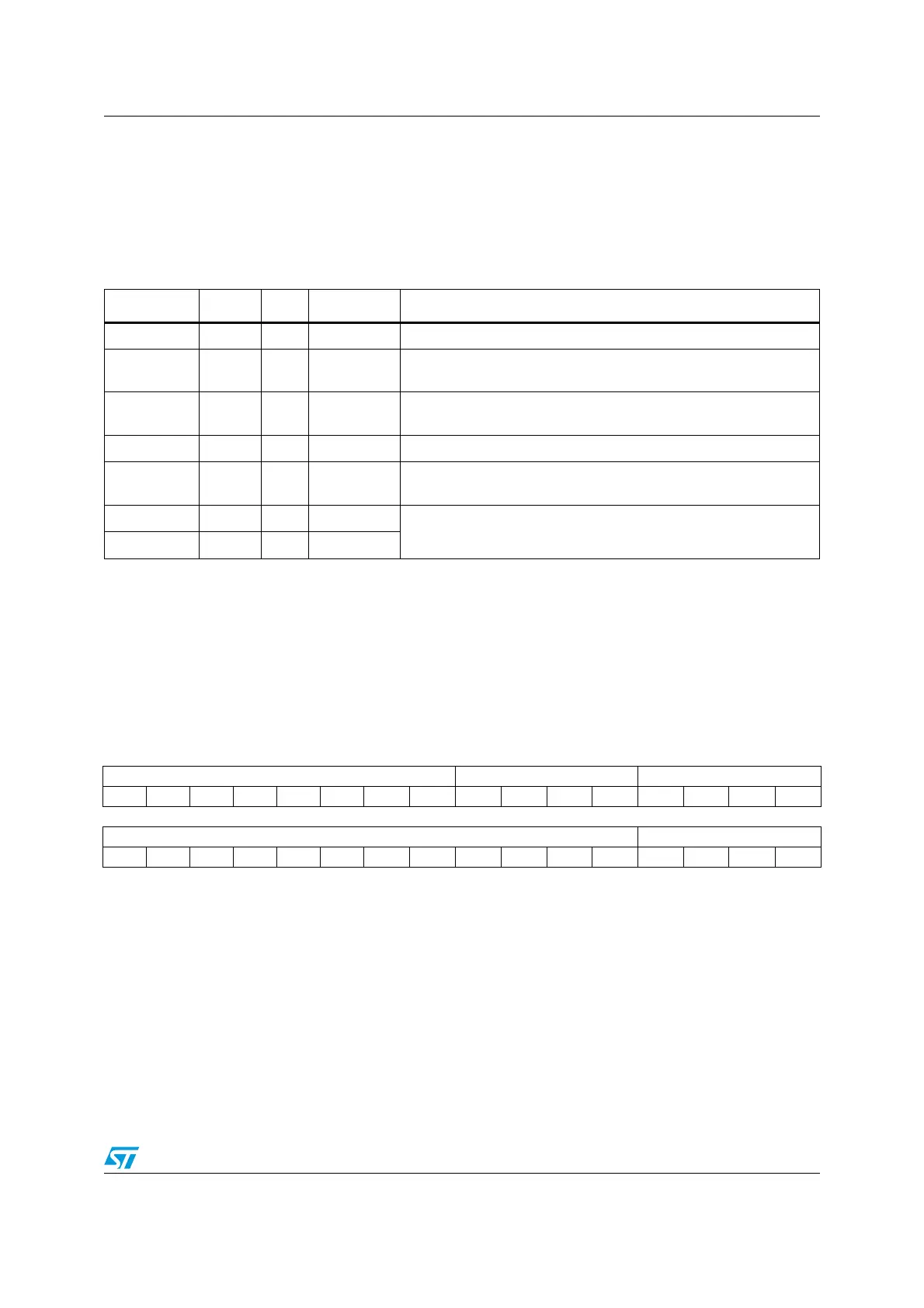

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Implementer Variant Constant

rrrrrr r r r r r r r r r r

1514131211109876543210

PartNo Revision

rrrrrr r r r r r r r r r r

Bits 31:24 Implementer: Implementer code

0x41: ARM

Bits 23:20 Variant: Variant number: The r value in the

Rnpn product revision identifier

0x0: revision 0

Bits 19:16 Constant: Constant that defines the architecture of the processor:

0xC: ARMv6-M architecture

Bits 15:4 PartNo: Part number of the processor

0xC20: Cortex-M0

Bits 3:0 Revision: The p value in the

Rnpn product revision identifier, indicates patch release.

0x0: patch 0

Loading...

Loading...