The STM32 Cortex-M0 instruction set PM0215

32/91 Doc ID 022979 Rev 1

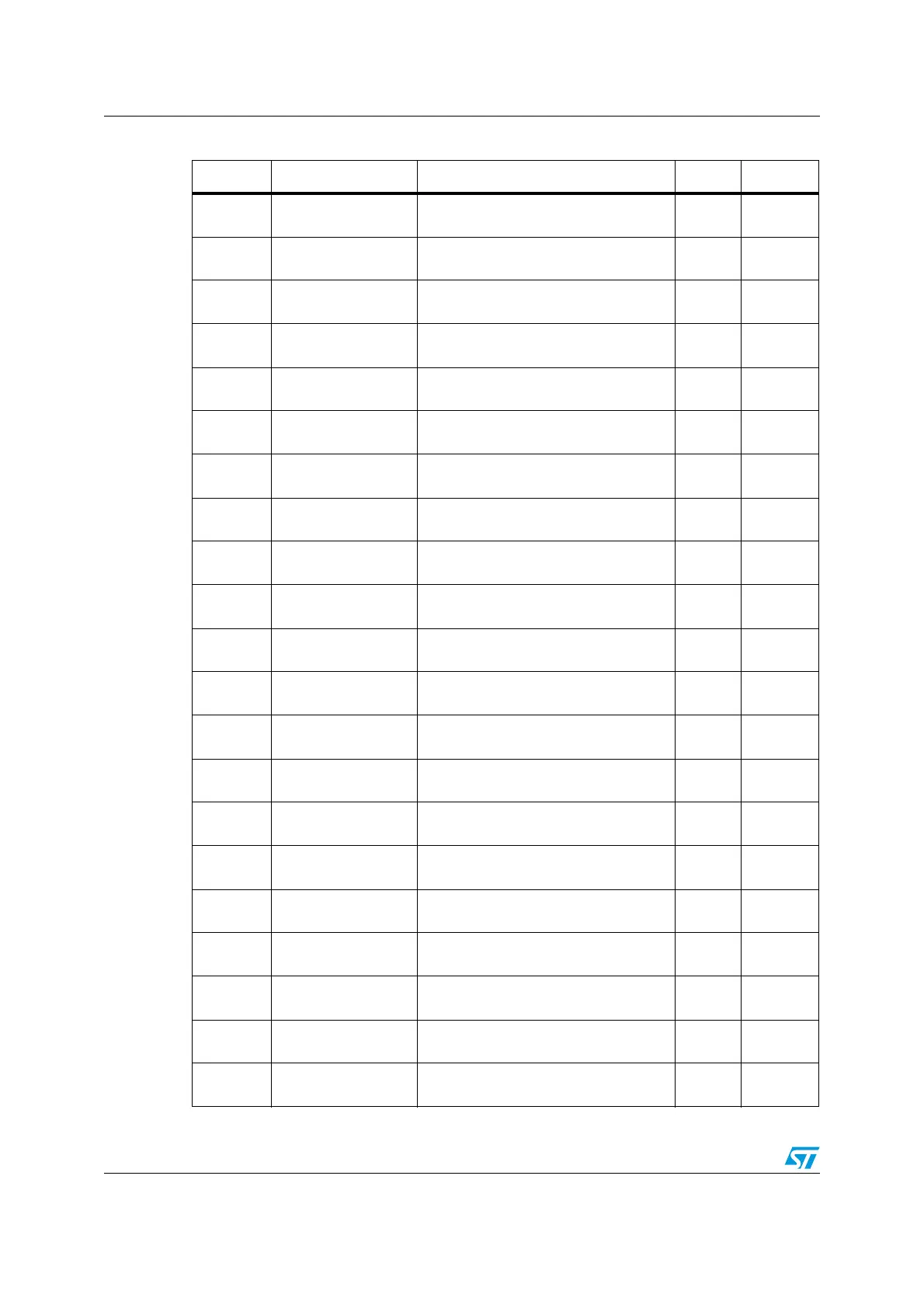

BICS {Rd,} Rn, Rm Bit clear N,Z

3.5.2 on

page 51

BKPT #imm Breakpoint -

3.7.1 on

page 61

BL label Branch with link -

3.6.1 on

page 59

BLX Rm Branch indirect with Link -

3.6.1 on

page 59

BX Rm Branch indirect -

3.6.1 on

page 59

CMN Rn, Rm Compare negative N,Z,C,V

3.5.4 on

page 53

CMP Rn, <Rm|#imm> Compare N,Z,C,V

3.5.4 on

page 53

CPSID i

Change processor state, disable

interrupts

-

3.7.2 on

page 62

CPSIE i

Change processor state, enable

interrupts

-

3.7.2 on

page 62

DMB - Data memory barrier -

3.7.3 on

page 63

DSB - Data synchronization barrier -

3.7.4 on

page 63

EORS {Rd,}

Rn, Rm Exclusive OR N,Z

3.5.2 on

page 51

ISB - Instruction synchronization barrier -

3.7.5 on

page 64

LDM Rn{!}, reglist Load multiple registers, increment after -

3.4.5 on

page 46

LDR Rt, label Load register from PC-relative address -

3.4.4 on

page 45

LDR Rt, [Rn, <Rm|#imm>] Load register with word -

3.4.3 on

page 44

LDRB Rt, [Rn, <Rm|#imm>] Load register with byte -

3.4.2 on

page 43

LDRH Rt, [Rn, <Rm|#imm>] Load register with halfword -

3.4.2 on

page 43

LDRSB Rt, [Rn, <Rm|#imm>] Load register with signed byte -

3.4.2 on

page 43

LDRSH Rt, [Rn, <Rm|#imm>] Load register with signed halfword -

3.4.2 on

page 43

LSLS {Rd,}

Rn, <Rs|#imm> Logical shift left N,Z,C

3.5.3 on

page 52

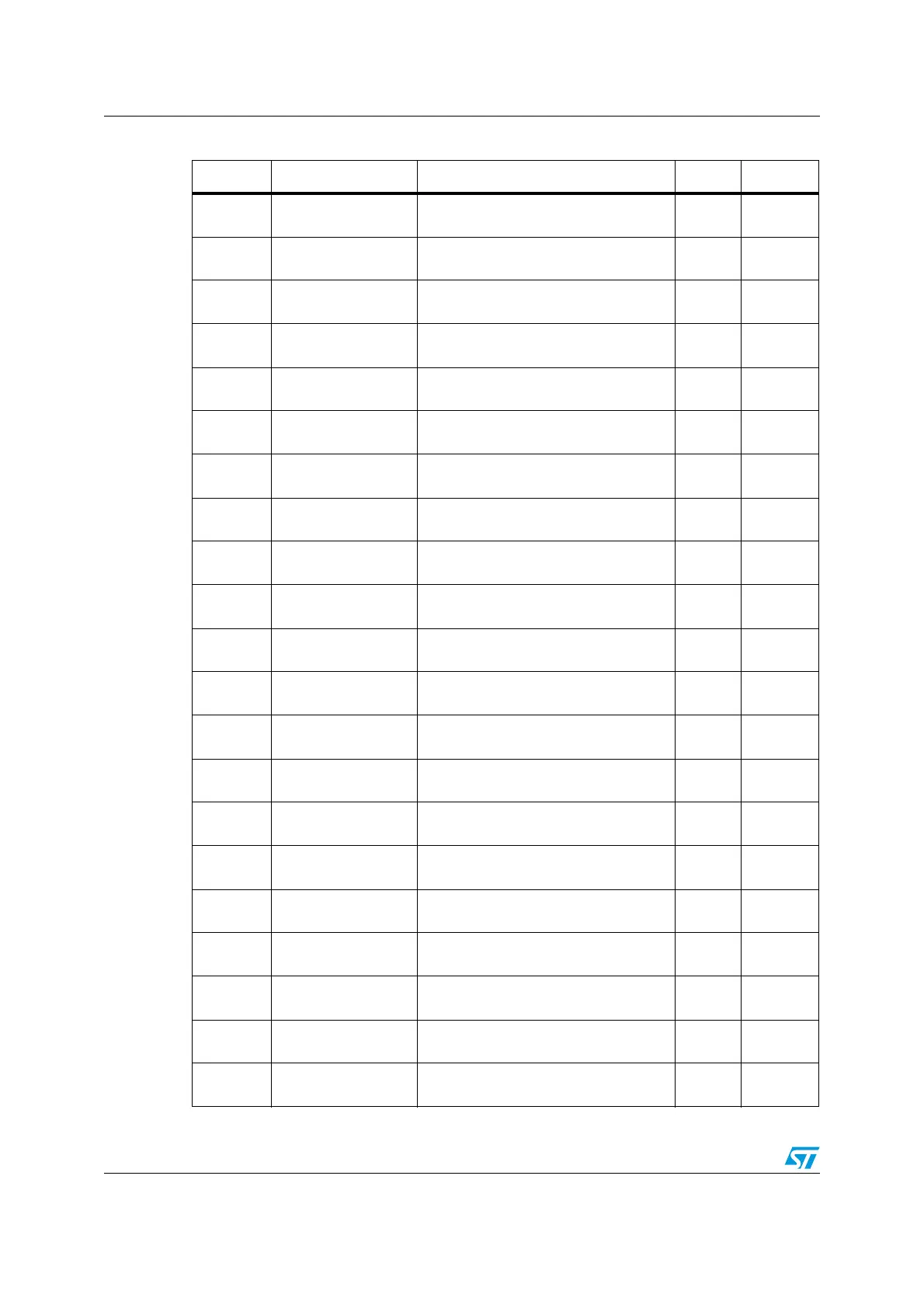

Table 14. Cortex-M0 instructions

Mnemonic Operands Brief description Flags Page

Loading...

Loading...