TOTAL- ACEXTREME® SIGNALS

Data Device Corporation DS-BU-67301B-G

www.ddc-web.com

1/14

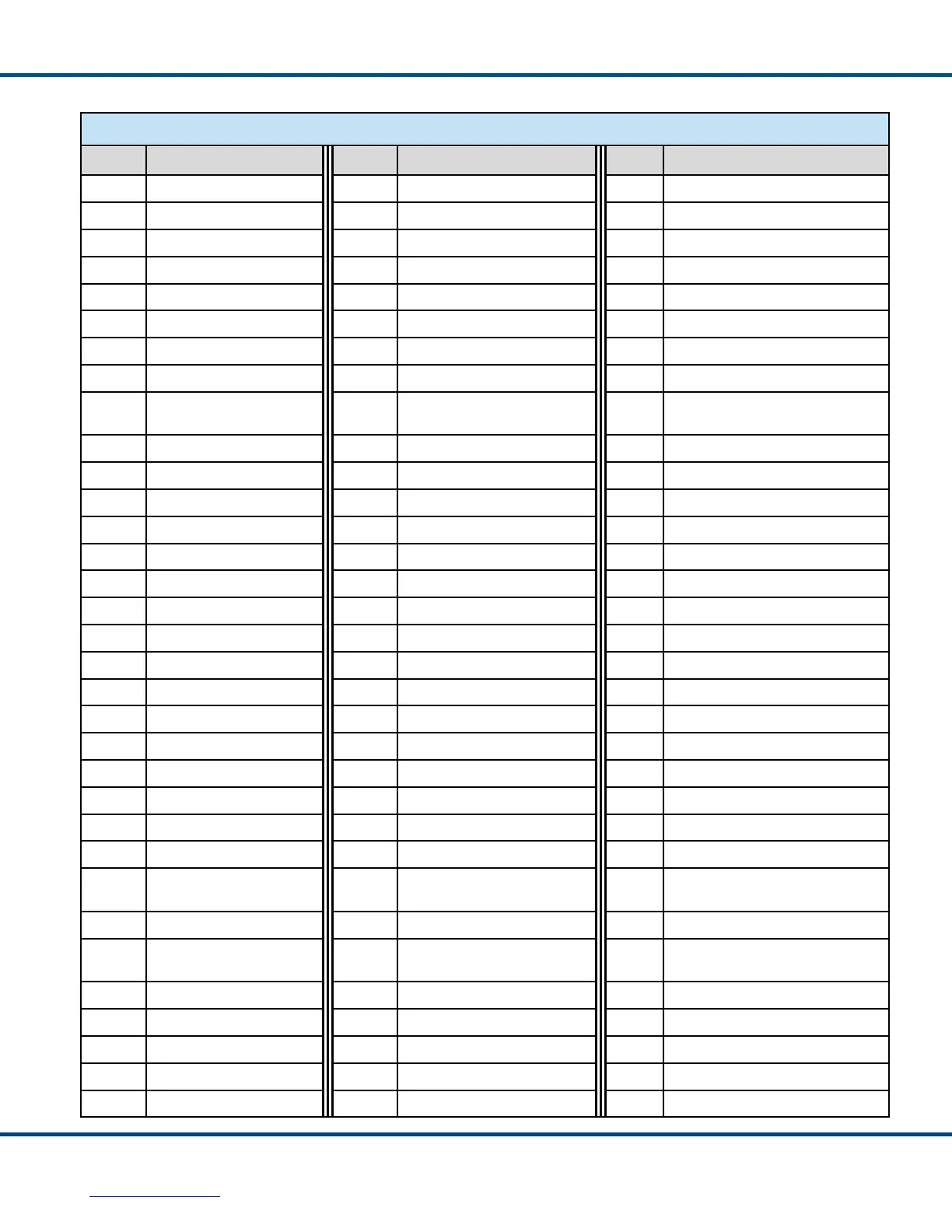

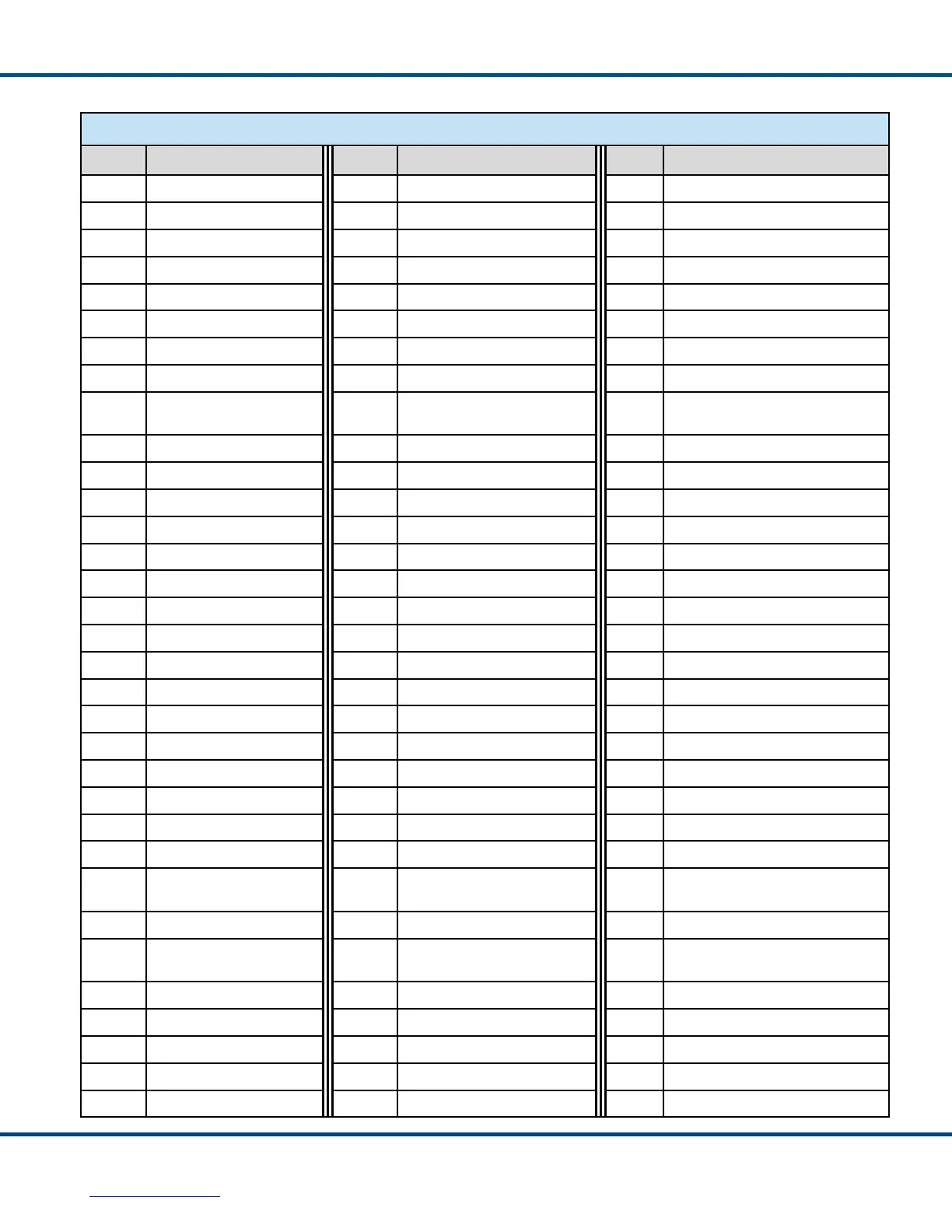

Table 26. Signal Pinout by Ball Location

BALL Signal Name BALL Signal Name BALL Signal Name

B12 GND_LOGIC H12 DISCRETE_IO_7 P12 GND_XCVR

B13 GND_LOGIC H13 RTADP P13 TX_INH_A

B14 GND_LOGIC H14 RTAD4 P14 TX_INH_B

B15 NC H15 NC P15 NC

B16 NC H16 NC P16 NC

B17 NC H17 NC P17 CHB_1553 (I/O)

B18 NC H18 NC P18 CHB_1553 (I/O)

C1 NC J1 DEVSEL#/CPU_ADDR(09) R1 nDATA_RDY

C2

PCI_AD(25)/CPU_DATA(

25) J2 SERR# R2 MEM_nREG

C3 IRDY#/CPU_ADDR(07) J3 TRDY#/CPU_ADDR(06) R3 ADDR_LAT

C4 +3.3V_LOGIC J4 C/BE[2]#/CPU_ADDR(02) R4 CPU_nLAST

C5 +3.3V_LOGIC J5 PCI_AD(17)/CPU_DATA(17) R5 GND_XCVR

C6 +3.3V_LOGIC J6 RD_nWR R6 GND_XCVR

C7 +3.3V_LOGIC J7 CPU_ASYNC_nSYNC R7 GND_XCVR

C8 +3.3V_LOGIC J8 RXDATA_IN_A R8 GND_XCVR

C9 +3.3V_LOGIC J9 RXDATA_IN_A_L R9 GND_XCVR

C10 nPOR J10 TXDATA_OUT_A R10 NC

C11 PCI_nCPU J11 TXDATA_OUT_A_L R11 GND_XCVR

C12 +3.3V_LOGIC J12 DISCRETE_IO_5 R12 GND_XCVR

C13 DISABLE_BIST J13 DISCRETE_IO_4 R13 nSINGEND

C14 DISABLE_BC J14 GND_LOGIC R14 nSSFLAG

C15 NC J15 NC R15 NC

C16 NC J16 NC R16 NC

C17 NC J17 NC R17 CHB_1553_L

C18 NC J18 NC R18 CHB_1553_L

D1

PCI_AD(26)/CPU_DATA(

26) K1 PCI_AD(15)/CPU_DATA(15) T1 NC

D2 IDSEL/CPU_ADDR(10) K2 PCI_AD(10)/CPU_DATA(10) T2 nSELECT

D3

PCI_AD(24)/CPU_DATA(

24) K3 PCI_AD(04)/CPU_DATA(04) T3 CPU_ADDR(14)

D4 GND_LOGIC K4 PCI_AD(01)/CPU_DATA(01) T4 CPU_ADDR(15)

D5 GND_LOGIC K5 C/BE[1]#/CPU_ADDR(01) T5 +3.3V_XCVR

D6 GND_LOGIC K6 DATA32_n16 T6 +3.3V_XCVR

D7 GND_LOGIC K7 POL_SEL T7 +3.3V_XCVR

D8 GND_LOGIC K8 RXDATA_OUT_A T8 +3.3V_XCVR

Loading...

Loading...