12 16-BIT PWM TIMER (T16E)

12-10

Seiko Epson Corporation

S1C17624/604/622/602/621 TECHNICAL MANUAL

Notes: • The clock generator (CLG) must be configured to supply PCLK to the peripheral modules be-

fore running the timer.

• Make sure the counter is halted before setting the count clock.

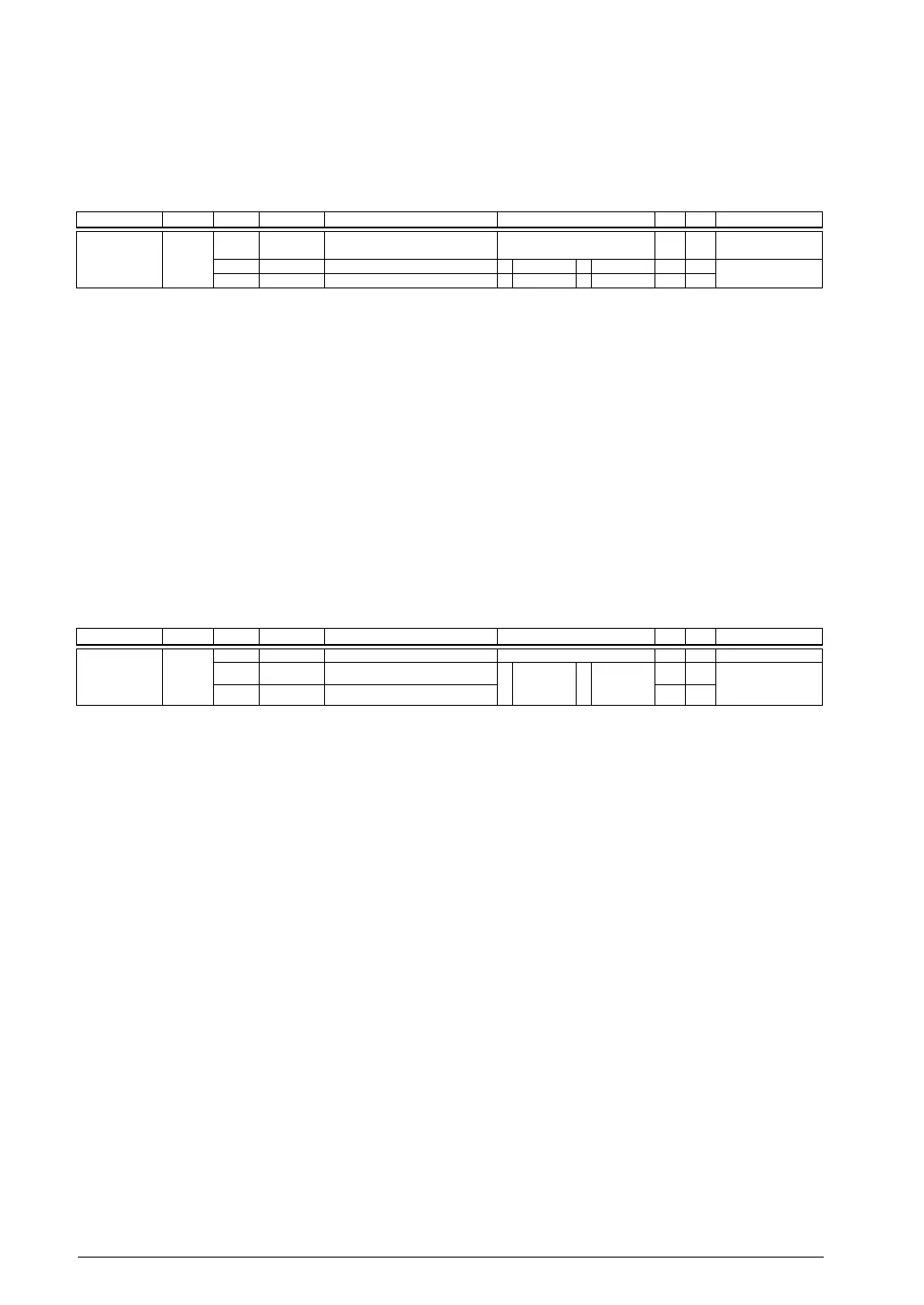

T16E Ch.x Interrupt Mask Register (T16E_IMSKx)

Register name Address Bit Name Function Setting Init. R/W Remarks

T16E Ch.x

Interrupt Mask

Register

(T16E_IMSKx)

0x530a

(16 bits)

D15–2

–

reserved – – – 0 when being read.

D1

CBIE

Compare B interrupt enable 1 Enable 0 Disable 0 R/W

D0

CAIE

Compare A interrupt enable 1 Enable 0 Disable 0 R/W

D[15:2] Reserved

D1 CBIE: Compare B Interrupt Enable Bit

Enables or disables compare B match interrupts.

1 (R/W): Interrupt enabled

0 (R/W): Interrupt disabled (default)

Setting CBIE to 1 enables compare B interrupt requests to the ITC. Setting it to 0 disables interrupts.

D0 CAIE: Compare A Interrupt Enable Bit

Enables or disables compare A

match interrupts.

1 (R/W): Interrupt enabled

0 (R/W): Interrupt disabled (default)

Setting CAIE to 1 enables compare A interrupt requests to the ITC. Setting it to 0 disables interrupts.

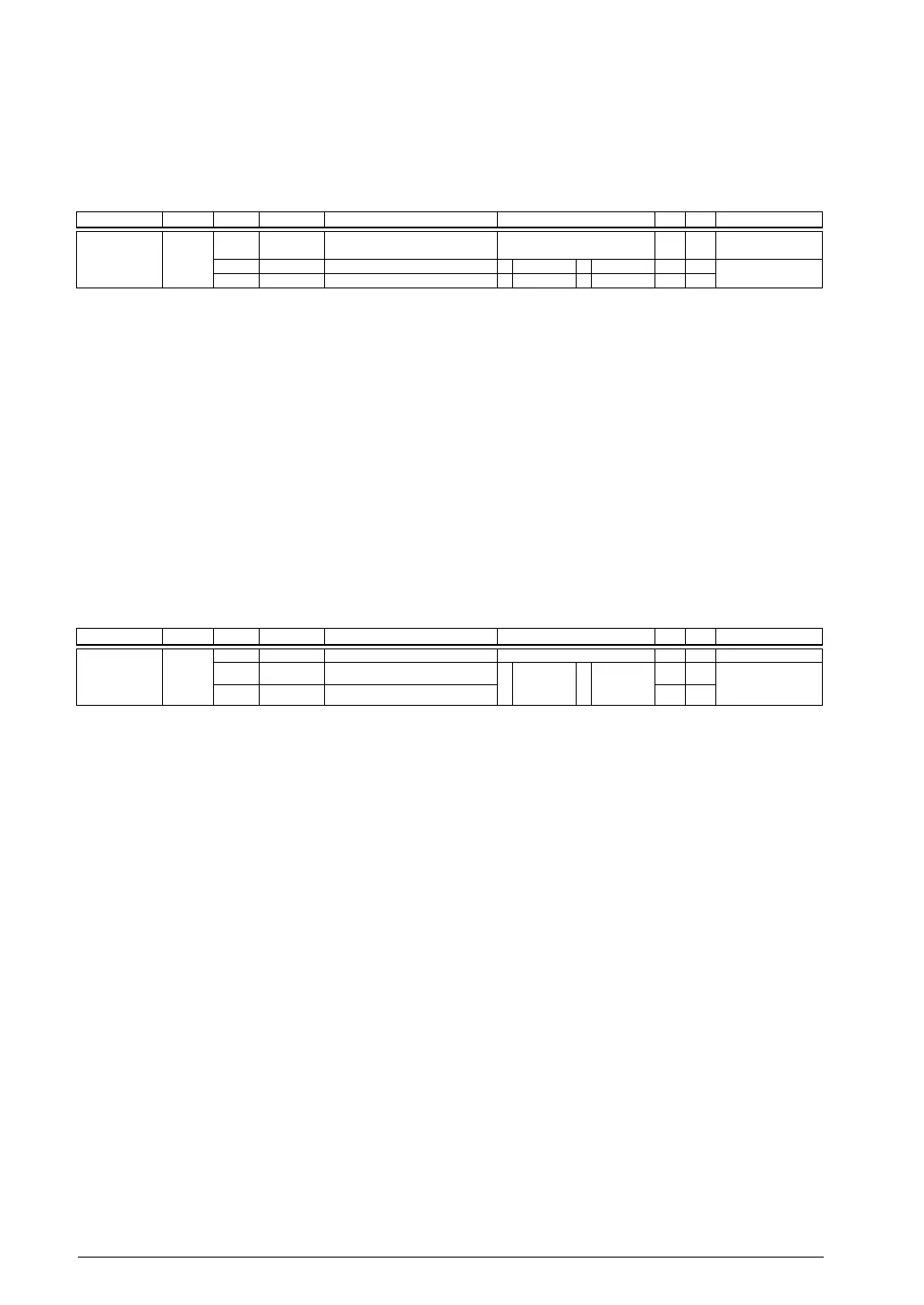

T16E Ch.x Interrupt Flag Register (T16E_IFLGx)

Register name Address Bit Name Function Setting Init. R/W Remarks

T16E Ch.x

Interrupt Flag

Register

(T16E_IFLGx)

0x530c

(16 bits)

D15–2

–

reserved – – – 0 when being read.

D1

CBIF

Compare B interrupt flag 1 Cause of

interrupt

occurred

0 Cause of

interrupt not

occurred

0 R/W Reset by writing 1.

D0

CAIF

Compare A interrupt flag 0 R/W

D[15:2] Reserved

D1 CBIF: Compare B Interrupt Flag Bit

Indicates whether the cause of compare B interrupt has occurred or not.

1 (R): Cause of interrupt has occurred

0 (R): No cause of interrupt has occurred (default)

1 (W): Flag is reset

0 (W): Ignored

CBIF

is a T16E interrupt flag that is set to 1 when the counter reaches the value set in the compare B

register. CBIF is reset by writing 1.

D0 CAIF: Compare A Interrupt Flag Bit

Indicates whether the cause of compare A interrupt has occurred or not.

1 (R): Cause of interrupt has occurred

0 (R): No cause of interrupt has occurred (default)

1 (W): Flag is reset

0 (W): Ignored

CAIF is a T16E interrupt flag that is set to 1 when the counter

reaches the value set in the compare A

register. CAIF is reset by writing 1.

Loading...

Loading...