21 I

2

C SLAVE (I2CS)

S1C17624/604/622/602/621 TECHNICAL MANUAL

Seiko Epson Corporation

21-15

D0 DA_STOP: Stop Condition Detect Bit

Indicates that a stop condition or a repeated start condition is detected.

1 (R/W): Detected

0 (R/W): Not detected (default)

If a stop condition or a repeated start condition is detected while the I2CS module is selected as the

slave device (SELECTED/I2CS_ASTAT register = 1), the I2CS module sets DA_STOP to 1. At the

same time, it initializes the I

2

C communication process.

When DA_STOP is set to

1, an interrupt signal is output to the ITC if the interrupt is enabled with

BSTAT_IEN/I2CS_ICTL register. This interrupt can be used to perform a terminate handling. After

DA_STOP is set to 1, it is reset to 0 by writing 1.

I

2

C Slave Access Status Register (I2CS_ASTAT)

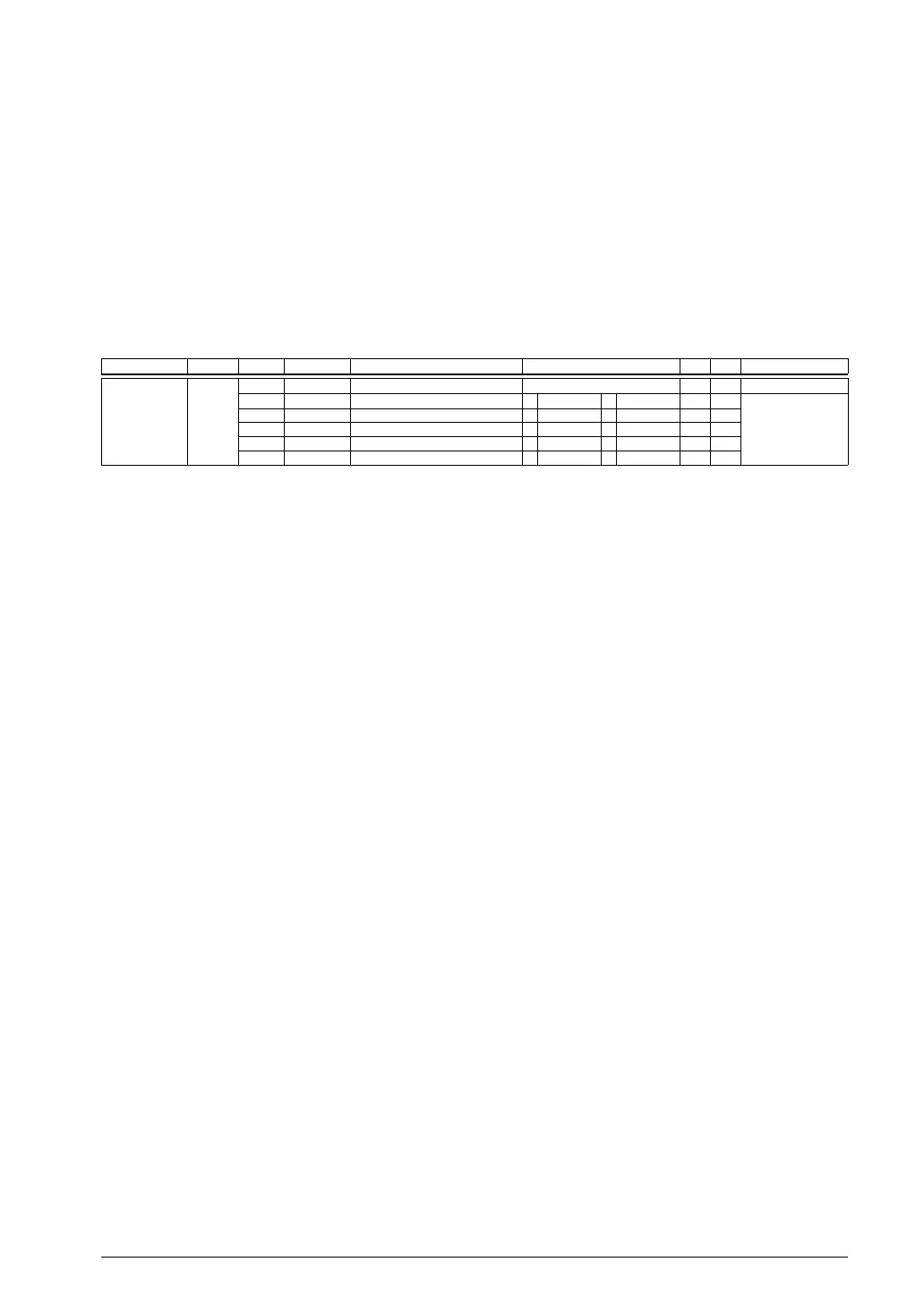

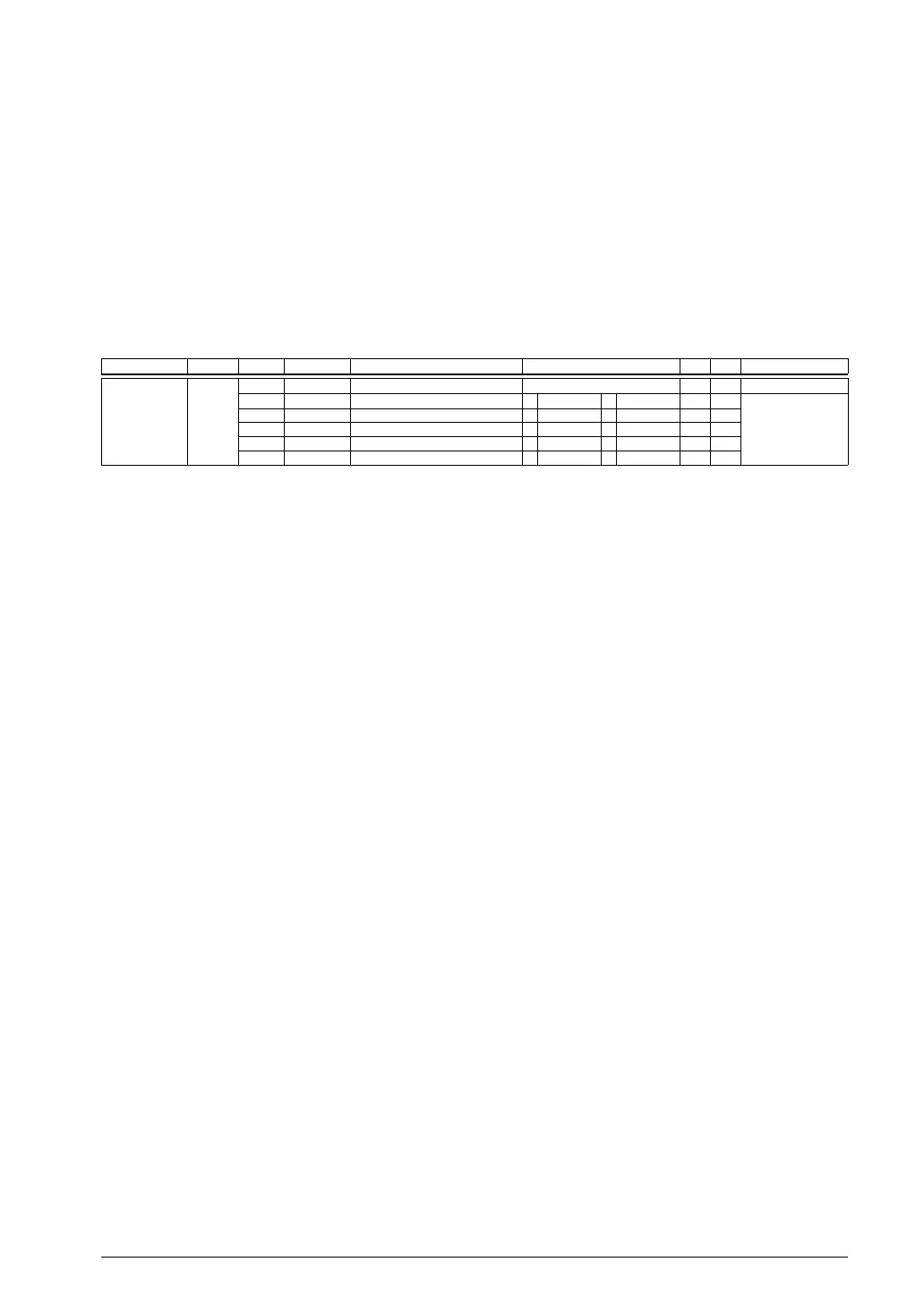

Register name Address Bit Name Function Setting Init. R/W Remarks

I

2

C Slave

Access Status

Register

(I2CS_ASTAT)

0x436a

(16 bits)

D15–5

–

reserved – – – 0 when being read.

D4

RXRDY

Receive data ready 1 Ready 0 Not ready 0 R

D3

TXEMP

Transmit data empty 1 Empty 0 Not empty 0 R

D2

BUSY

I

2

C bus status 1 Busy 0 Free 0 R

D1

SELECTED

I

2

C slave select status 1 Selected 0

Not selected

0 R

D0

R/W

Read/write direction 1 Output 0 Input 0 R

D[15:5] Reserved

D4 RXRDY: Receive Data Ready Bit

Indicates that the received data is ready to read.

1 (R): Received data ready

0 (R): No received data (default)

When the received data is loaded to th

e I2CS_RECV register, RXRDY is set to 1. At the same time, an

interrupt signal is output to the ITC if the interrupt is enabled with RXRDY_IEN/I2CS_ICTL register.

This interrupt can be used to read the received data from the I2CS_RECV register.

After RXRDY is set to 1, it is reset to 0 when the I2CS_RECV register is read.

D3 TXEMP: Transmit Data Empty Bit

Indicates that transmit data can be written.

1 (R): Transmit data empty (da

ta can be written)

0 (R): Transmit data still stored (data cannot be written) (default)

When the transmit data written to the I2CS_TRNS register is sent, TXEMP is set to 1. At the same

time, an interrupt signal is output to the ITC if the interrupt is enabled with TXEMP_IEN/I2CS_ICTL

register. This interrupt can be used to write the next transmit data to the I2CS_TRNS register.

After TXEMP is set

to 1, it is reset to 0 when data is written to the I2CS_TRNS register.

D2 BUSY: I

2

C Bus Status Bit

Indicates the I

2

C bus status.

1 (R): Bus busy status

0 (R): Bus free status (default)

When the I2CS module detects a start condition or detects that the SCL1 or SDA1 signal goes low,

BUSY is set to 1 to indicate that the I

2

C bus enters busy status. The slave select status whether this

module is selected as the slave device o

r not does not affect the BUSY status. After BUSY is set to 1, it

is reset to 0 when a STOP condition is detected.

D1 SELECTED: I

2

C Slave Select Status Bit

Indicates that this module is selected as the I

2

C slave device.

1 (R): Selected

0 (R): Not selected (default)

When the slave address that is set in this module is received, SELECTED is set to 1 to indicate that this

module is selected as the I

2

C slave device. After SELECTED is set to 1, it is reset to 0 when a stop con-

dition or a repeated start condition is detected.

Loading...

Loading...