24 A/D CONVERTER (ADC10)

24-2

Seiko Epson Corporation

S1C17624/604/622/602/621 TECHNICAL MANUAL

ADC10 Input Pins24.2

Table 24.2.1 lists the ADC10 input pins.

2.1 List of ADC10 Input PinsTable 24.

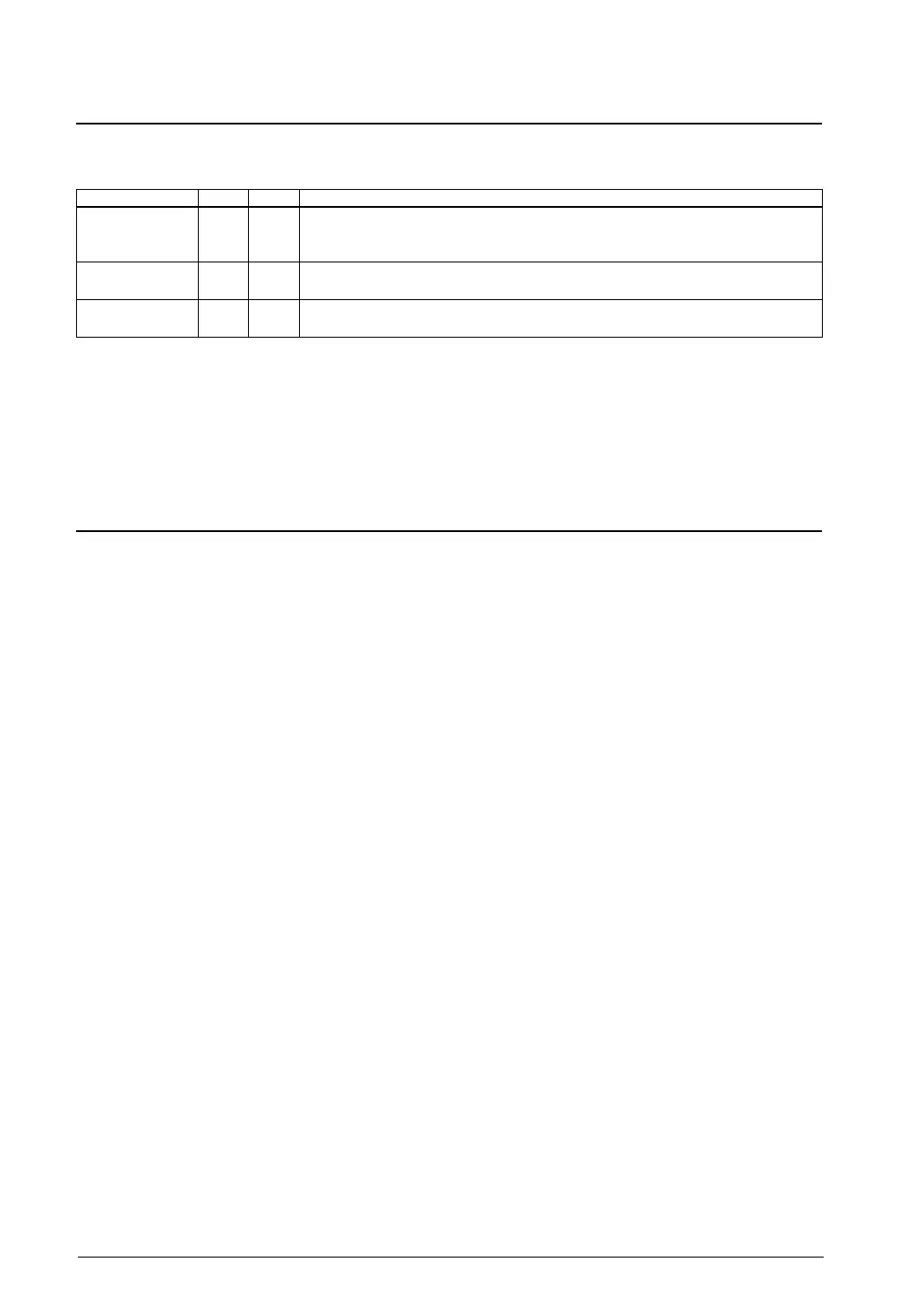

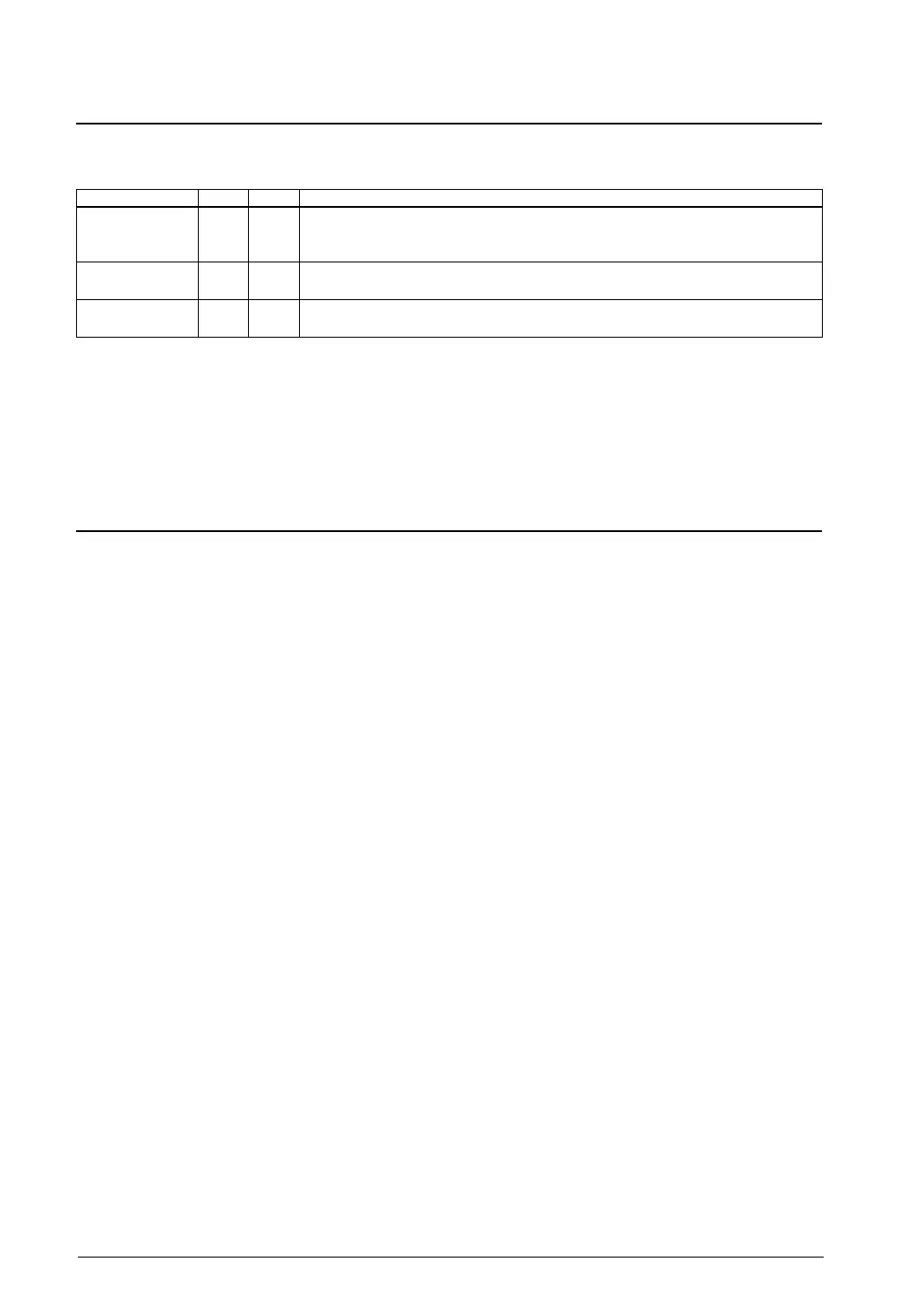

Pin name I/O Qty Function

AIN[7:0] I 8 Analog signal input pins AIN0 (Ch.0) to AIN7 (Ch.7) (see Note below)

Input the analog signals to be A/D converted. The analog input voltage AVIN must

be within the range of VSS ≤ AVIN ≤ AVDD (= VDD).

#ADTRG I 1 External trigger input pin

Input a trigger signal to start A/D conversion from an external source.

AV

DD – 1 Analog power-supply pin (AVDD = VDD)

Always supply the VDD voltage even if the A/D converter is not used.

Note: The pins go to high impedance status when the port function is switched.

The A/D converter input pins (AIN[7:0], #ADTRG) are shared with I/O ports and are initially set as general pur-

pose I/O port pins. The pin functions must be switched using the port function select bits to use the general purpose

I/O port pins as A/D converter input pins.

For d

etailed information on pin function switching, see the “I/O Ports (P)” chapter.

A/D Converter Settings24.3

Make the following settings before starting A/D conversion.

(1) Set the analog input pins. See Section 24.2.

(2) Set the A/D conversion clock.

(3) Select the A/D conversion start and end channels.

(4) Select the A/D conversion mode.

(5) Select the A/D conversion trigger source.

(6) Set the sampling

time.

(7) Select the conversion result storing mode.

(8) When using A/D converter interrupts, set interrupt conditions. See Section 24.5.

Note: Make sure the A/D converter is disabled (ADEN/ADC10_CTL register = 0) before changing the

above settings. Changing the settings while the A/D converter is enabled may cause a malfunc-

tion.

A/D Conversion Clock Setting24.3.1

To use the A/D converter, the clock used in the A/D converter must be supplied by turning on the peripheral module

clock (PCLK) output from the clock generator (CLG). For more information on clock control, see the “Clock Gen-

erator (CLG)” chapters.

The A/D conversion is generated by dividing PCLK. The division ratio can be selected from the 15 types shown in

Table 24.3.1.1 using ADDF[3:0]/ADC_DIV register.

Note: For the A/D conversion clo

ck frequency range that can be used for this A/D converter, see “A/D

Converter Characteristics” in the “Electrical Characteristics” chapter.

Loading...

Loading...