3 MEMORY MAP

S1C17624/604/622/602/621 TECHNICAL MANUAL

Seiko Epson Corporation

3-7

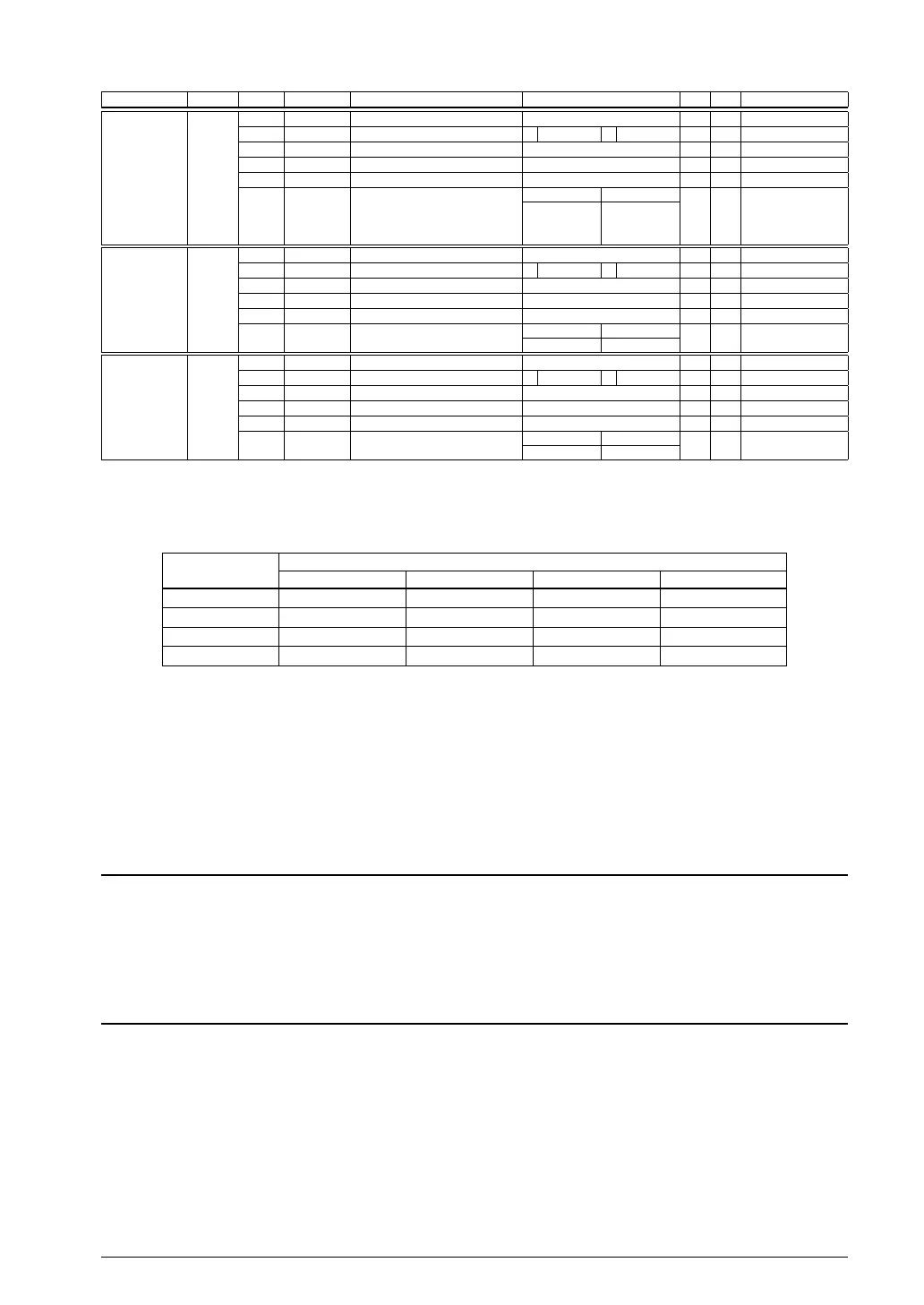

Register name Address Bit Name Function Setting Init. R/W Remarks

IRAM Size

Select

Register

(MISC_IRAMSZ)

(S1C17622)

0x5326

(16 bits)

D15–9

–

reserved – – – 0 when being read.

D8

DBADR

Debug base address select 1 0x0 0 0xfffc00 0 R/W

D7

–

reserved – – – 0 when being read.

D6–4

–

reserved – – –

0x1 when being read.

D3

–

reserved – – – 0 when being read.

D2–0

IRAMSZ[2:0]

IRAM size select IRAMSZ[2:0] Size 0x1 R/W

0x3

0x2

Other

2KB

4KB

reserved

IRAM Size

Select

Register

(MISC_IRAMSZ)

(S1C17602)

0x5326

(16 bits)

D15–9

–

reserved – – – 0 when being read.

D8

DBADR

Debug base address select 1 0x0 0 0xfffc00 0 R/W

D7

–

reserved – – – 0 when being read.

D6–4

–

reserved – – –

0x2 when being read.

D3

–

reserved – – – 0 when being read.

D2–0

IRAMSZ[2:0]

IRAM size select IRAMSZ[2:0] Size 0x2 R/W

0x7–0x0 reserved

IRAM Size

Select

Register

(MISC_IRAMSZ)

(S1C17621)

0x5326

(16 bits)

D15–9

–

reserved – – – 0 when being read.

D8

DBADR

Debug base address select 1 0x0 0 0xfffc00 0 R/W

D7

–

reserved – – – 0 when being read.

D6–4

–

reserved – – –

0x2 when being read.

D3

–

reserved – – – 0 when being read.

D2–0

IRAMSZ[2:0]

IRAM size select IRAMSZ[2:0] Size 0x2 R/W

0x7–0x0 reserved

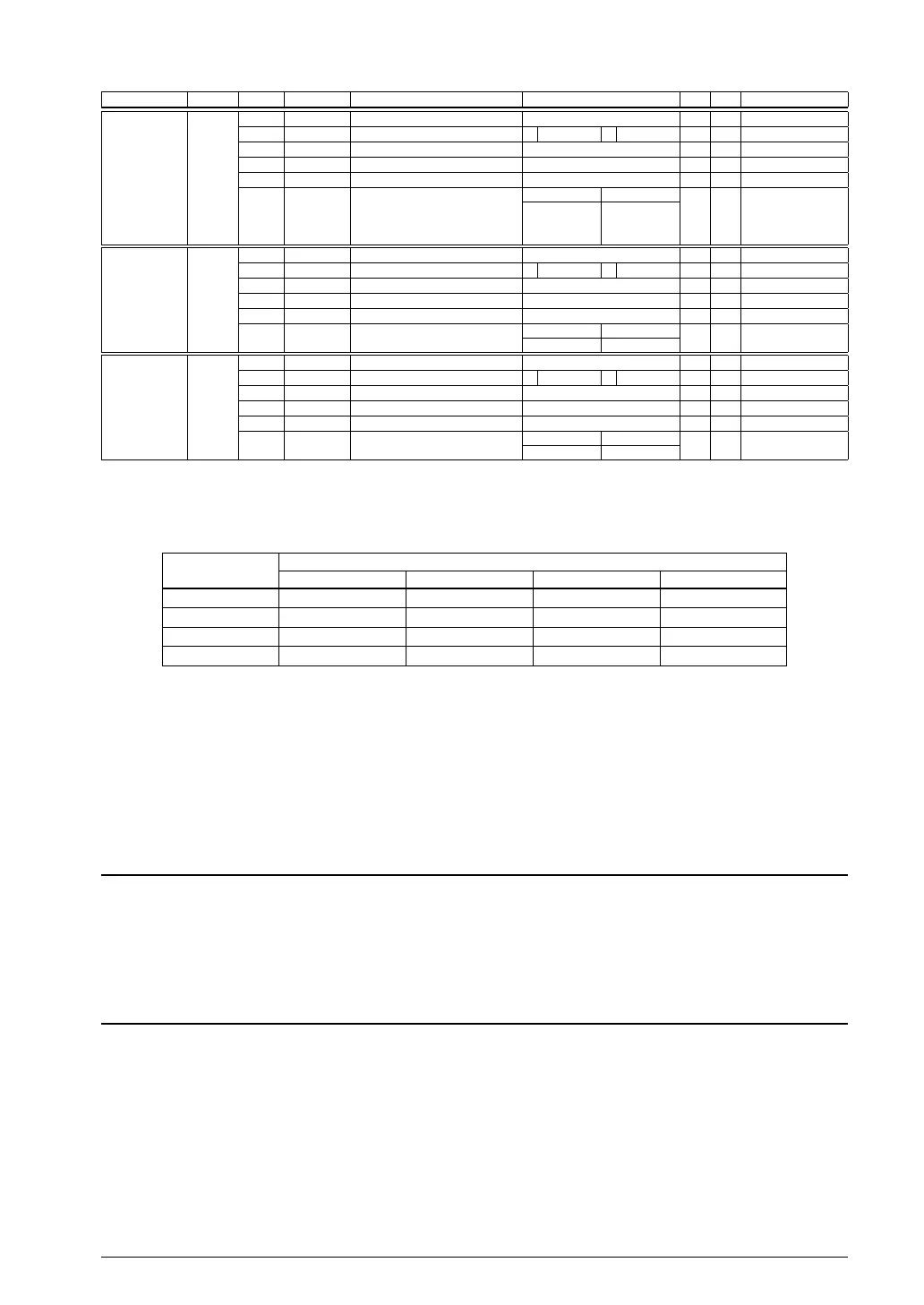

D[2:0] IRAMSZ[2:0]: IRAM Size Select Bits

Selects the internal RAM size used.

3.1.2 Selecting Internal RAM SizeTable 3.

IRAMSZ[2:0]

Internal RAM size

S1C17624/604 S1C17622 S1C17602 S1C17621

0x3 2KB 2KB Reserved Reserved

0x2 4KB 4KB Reserved (default) Reserved (default)

0x1 8KB (default) Reserved (default) Reserved Reserved

Other Reserved Reserved Reserved Reserved

Notes: • The MISC_IRAMSZ register is write-protected. The write-protection must be overridden by

writing 0x96 to the MISC_PROT register. Note that the MISC_PROT register should normal

ly

be set to a value other than 0x96, except when writing to the MISC_IRAMSZ register. Unnec-

essary programs may result in system malfunctions.

• In the S1C17602/621, do not alter the IRAMSZ[2:0]/MISC_IRAMSZ register setting from the

default value.

Display RAM Area3.4

The display RAM for the on-chip LCD driver is located in the 56-byte area (S1C17624/622) or 40-byte area

(S1C17604/602/621) beginni

ng with address 0x53c0 in the internal peripheral area. The display RAM is accessed

in one cycle as a 16-bit device. It can be used as a general-purpose RAM when it is not used for display. See the

“Display Memory” section in the “LCD Driver (LCD)” chapter for specific information on the display memory.

Internal Peripheral Area3.5

The I/O and control registers for the internal peripheral modules are located in the 1K-byte area beginning with ad-

dress 0x4000 and the 4K-byte area beginning with address 0x5000.

For details of each control register, see the I/O register list in Appendix or description for each peripheral module.

Internal Peripheral Area 1 (0x4000–)3.5.1

The internal peripheral area 1 beginning with address 0x4000 contains the I/O memory for the peripheral functions

listed below

and this area can be accessed in one cycle.

• MISC register (MISC, 8-bit device)

• UART (UART, 8-bit device)

Loading...

Loading...