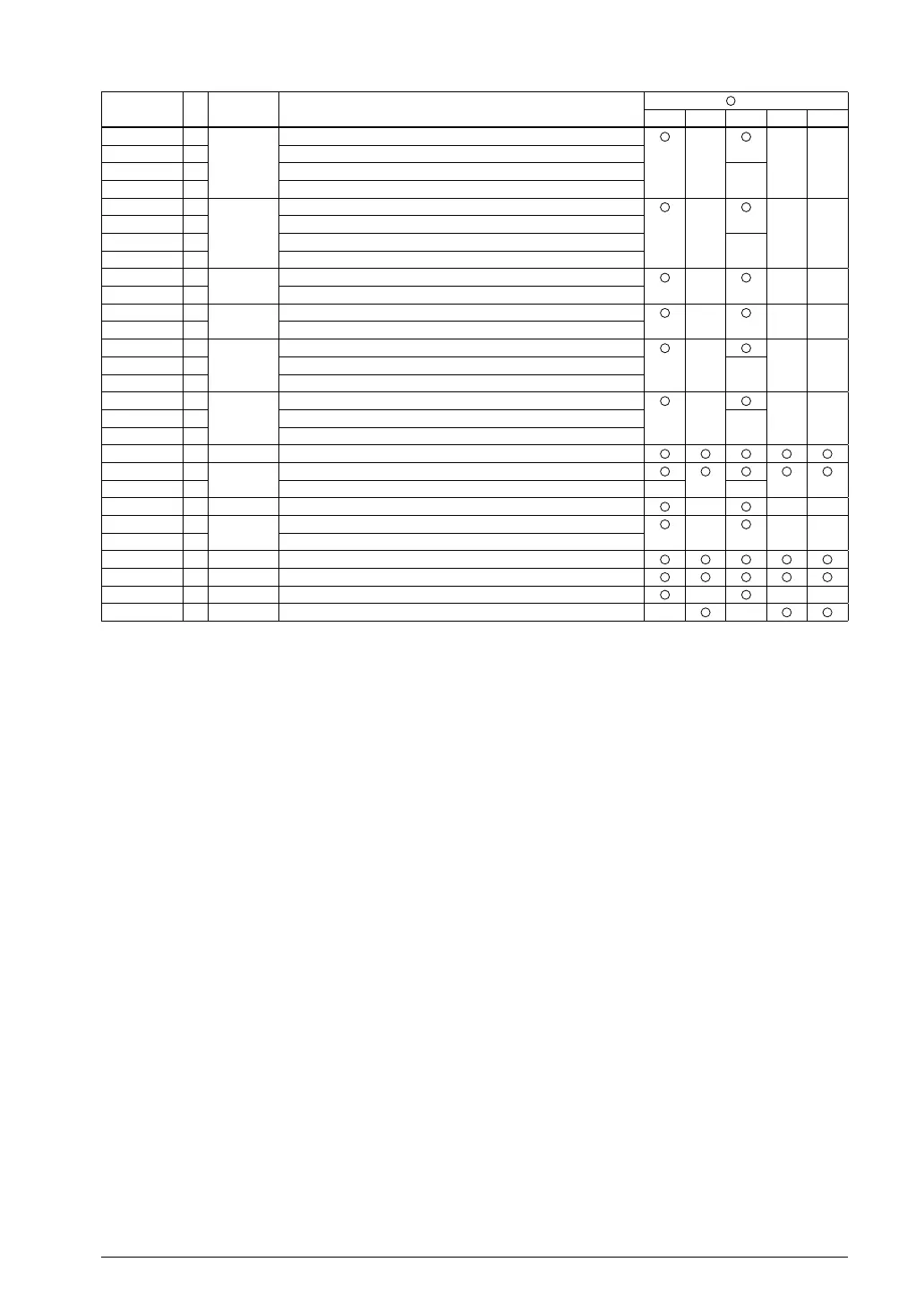

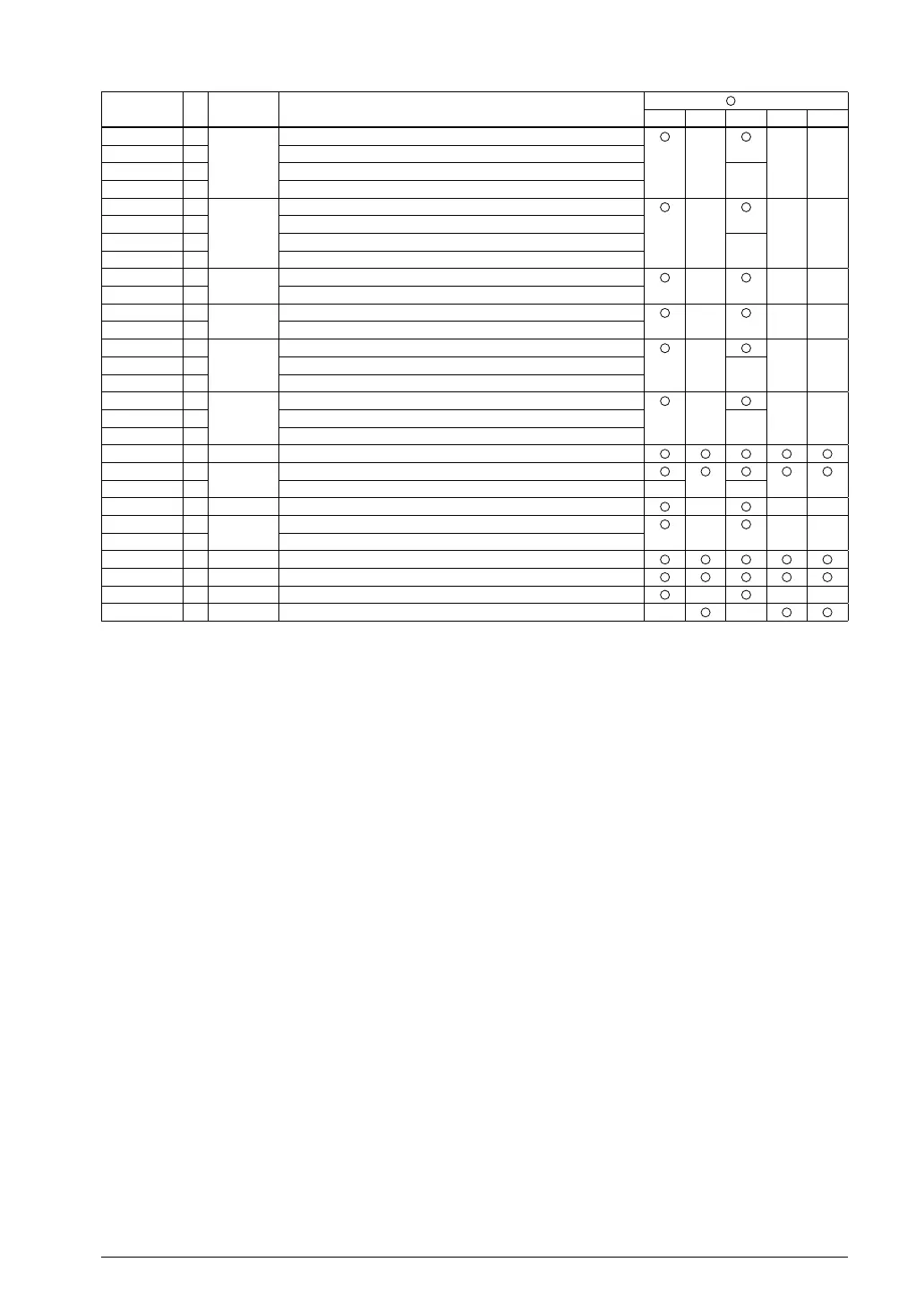

1 OVERVIEW

S1C17624/604/622/602/621 TECHNICAL MANUAL

Seiko Epson Corporation

1-19

Name I/O

Default

status

Function

Available ( )/unavailable (–)

17624 17604 17622 17602 17621

P51

I/O I (Pull-up) I/O port pin

– – –

SOUT1 O UART Ch.1 data output pin

TOUTA5 O T16A2 Ch.0 TOUT A signal output pin –

CAPA5 I T16A2 Ch.0 capture A trigger signal input pin

P52

I/O I (Pull-up) I/O port pin

– – –

SIN1 I UART Ch.1 data input pin

TOUTB5 O T16A2 Ch.0 TOUT B signal output pin –

CAPB5 I T16A2 Ch.0 capture B trigger signal input pin

P53

I/O I (Pull-up) I/O port pin

– – –

#BFR I I

2

C slave bus free request input pin

P54

I/O I (Pull-up) I/O port pin

– – –

LFRO O LCD frame signal output pin

P55

I/O I (Pull-up) I/O port pin

– – –

TOUTA6 O T16A2 Ch.1 TOUT A signal output pin –

CAPA6 I T16A2 Ch.1 capture A trigger signal input pin

P56

I/O I (Pull-up) I/O port pin

– – –

TOUTB6 O T16A2 Ch.1 TOUT B signal output pin –

CAPB6 I T16A2 Ch.1 capture B trigger signal input pin

SEG0–35

O O (L) LCD segment output pins

SEG36–39

O O (L) LCD segment output pins

COM7–4 O LCD common output pins – –

SEG40–51

O O (L) LCD segment output pins

– – –

SEG52–55

O O (L) LCD segment output pins

– – –

COM7–4 O LCD common output pins

COM0–3

O O (L) LCD common output pins

#RESET

I I (Pull-up) Initial reset input pin

TEST

I I Test input pin (Connect to V

SS for normal operation.) – – –

#TEST

I I Test input pin (Connect to V

DD for normal operation.) – –

Note: DCLK pin initial status

The DCLK pin of the S1C17624/604/622 goes high after the #RESET pin is set to 1 (after reset

status is canceled). The DCLK pin must be set to low with the pull-down resistor in the IC while

the #RESET pin is set to 0 (reset status), therefore do not connect any circuit such as a pull-up

resistor that may set the pin to high.

The S1C17602/621 DCLK pin goes high while the

#RESET pin is set to 0 (reset status).

Loading...

Loading...