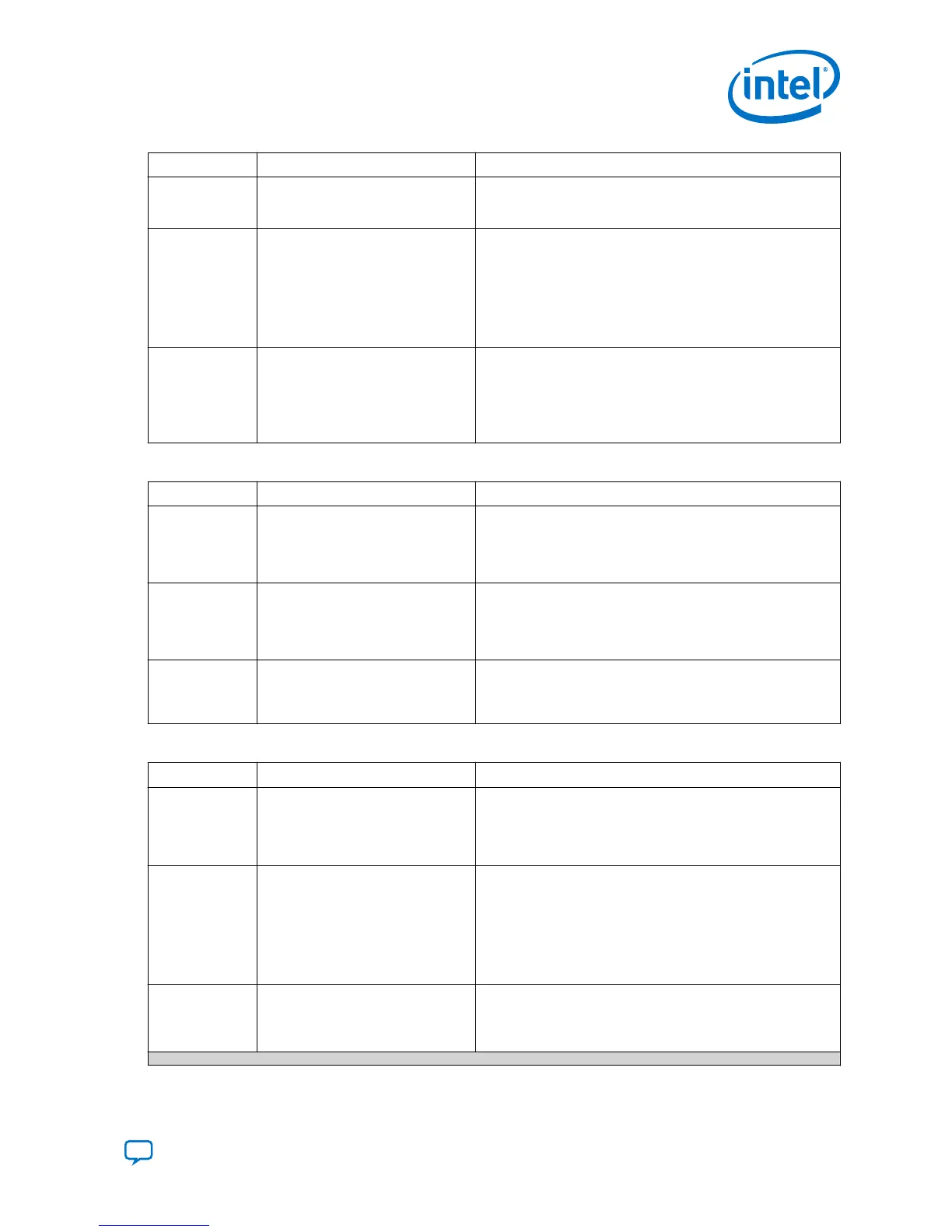

Options Value Description

For dual P30/P33 CFI flash, select the density that is equivalent

to the sum of the density of two flash memories. For example,

if you use two 512-Mb CFI flashes, you must select CFI 1 Gbit.

Flash interface

data width

CFI Parallel Flash:

• 8

• 16

• 32

Specifies the flash data width in bits. The flash data width

depends on the flash memory device you use. For multiple

flash memory device support, the data width must be the same

for all connected flash memory devices.

Select the flash data width that is equivalent to the sum of the

data width of two flash memories. For example, if you are

targeting dual P30 or P33 solution, you must select 32 bits

because each CFI flash data width is 16 bits.

User control

flash_nreset

pin

• On

• Off

Creates a flash_nreset pin in the PFL II IP core to connect

to the reset pin of the flash memory device. A low signal resets

the flash memory device. In burst mode, this pin is available by

default.

When using a Cypress GL flash memory, connect this pin to the

RESET# pin of the flash memory.

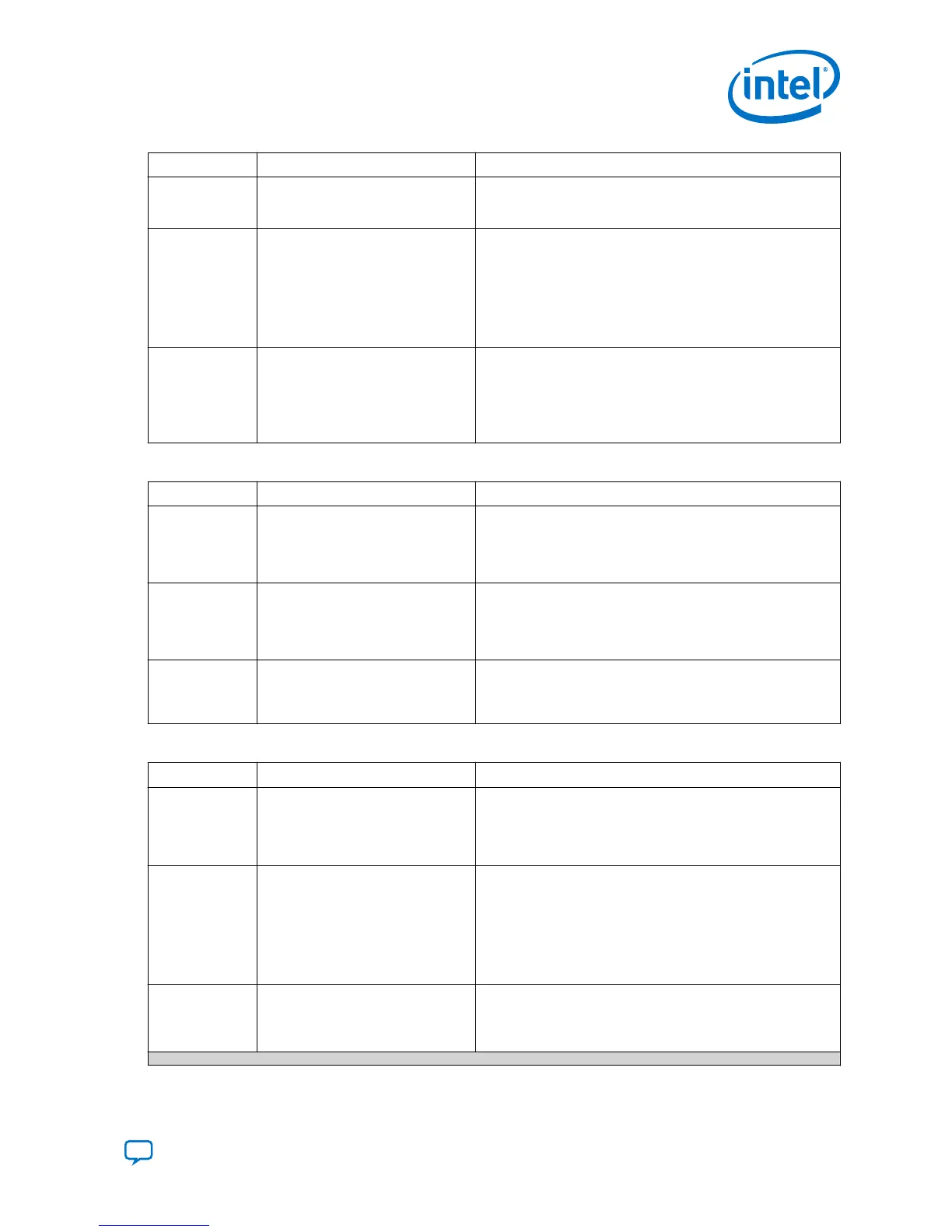

Table 20. PFL II Flash Programming Parameters

Options Value Description

Flash

programming IP

optimization

• Area

• Speed

Specifies the flash programming IP optimization. If you

optimize the PFL II IP core for speed, the flash programming

time is shorter, but the IP core uses more LEs. If you optimize

the PFL II IP core for area, the IP core uses less LEs, but the

flash programming time is longer.

FIFO size — Specifies the FIFO size if you select Speed for flash

programming IP optimization. The PFL II IP core uses

additional LEs to implement FIFO as temporary storage for

programming data during flash programming. With a larger

FIFO size, programming time is shorter.

Add Block-CRC

verification

acceleration

support

• On

• Off

Adds a block to accelerate verification.

Table 21. PFL II FPGA Configuration Parameters

Options Value Description

External clock

frequency

— Specifies the user-supplied clock frequency for the IP core to

configure the FPGA. The clock frequency must not exceed two

times the maximum clock (AVST_CLK) frequency acceptable by

the FPGA for configuration. The PFL II IP core can divide the

frequency of the input clock maximum by two.

Flash access

time

— Specifies the access time of the flash. You can get the

maximum access time that a flash memory device requires

from the flash datasheet. Intel recommends specifying a flash

access time that is the same as or longer than the required

time.

For CFI parallel flash, the unit is in ns and for NAND flash, the

unit is in us. NAND flash uses page instead of byte and requires

more access time. This option is disabled for quad SPI flash.

Option bits byte

address

— Specifies the start address in which the option bits are stored in

the flash memory. The start address must reside on an 8-KB

boundary.

See related for more information about option bits.

continued...

3. Intel Stratix 10 Configuration Schemes

UG-S10CONFIG | 2018.11.02

Send Feedback

Intel Stratix 10 Configuration User Guide

47

Loading...

Loading...