Point Grey Flea3 USB 3.0 Technical Reference Appendix A: Control and Status Registers

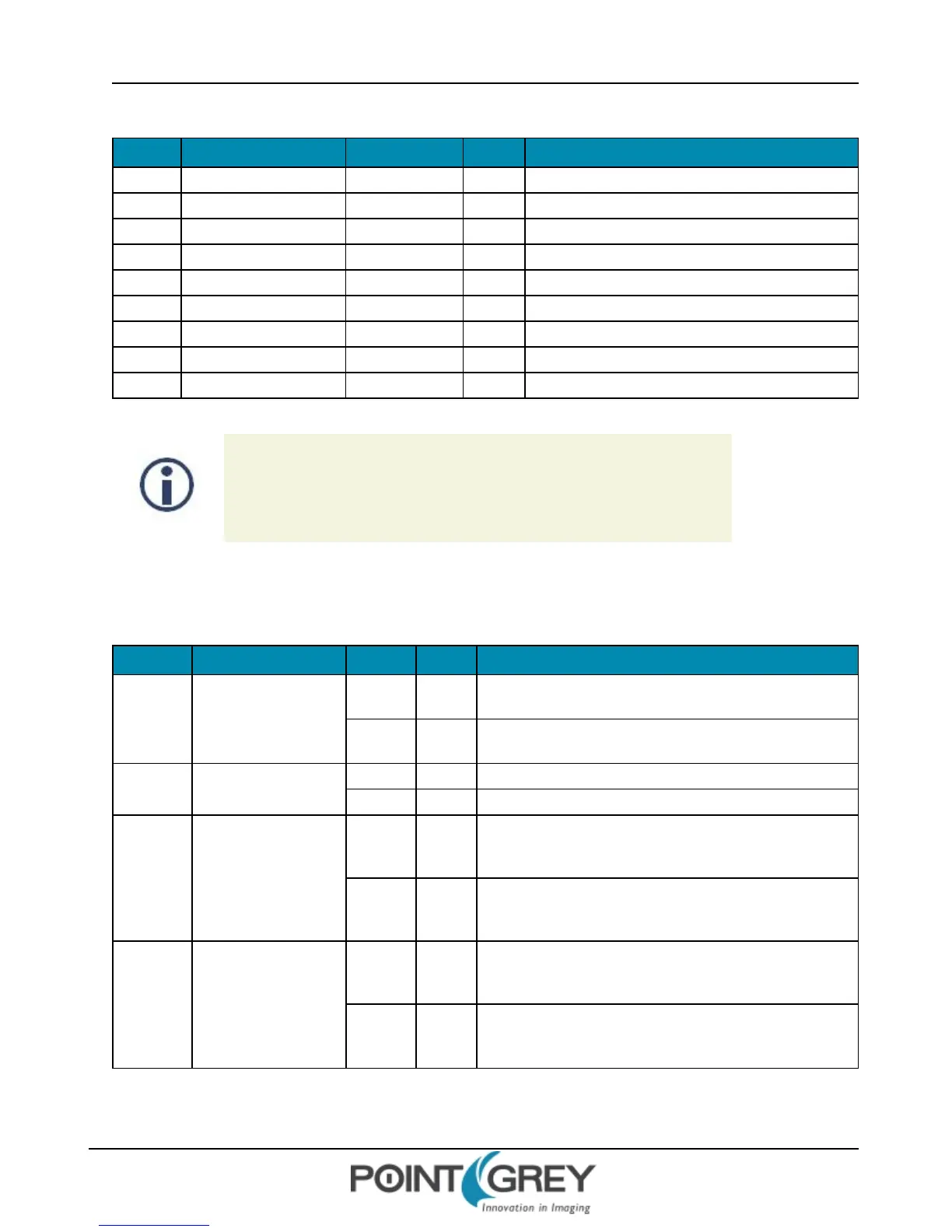

Table A.1: Custom Video Mode Inquiry Register Offset Addresses

Offset Name Field Bit Description

2E0h V_CSR_INQ_7_0 Mode_0 [0-31] 32-bit offset for Mode 0

2E4h V_CSR_INQ_7_1 Mode_1 [0-31] 32-bit offset for Mode 1

2E8h V_CSR_INQ_7_2 Mode_2 [0-31] 32-bit offset for Mode 2

2ECh V_CSR_INQ_7_3 Mode_3 [0-31] 32-bit offset for Mode 3

2F0h V_CSR_INQ_7_4 Mode_4 [0-31] 32-bit offset for Mode 4

2F4h V_CSR_INQ_7_5 Mode_5 [0-31] 32-bit offset for Mode 5

2F8h V_CSR_INQ_7_6 Mode_6 [0-31] 32-bit offset for Mode 6

2FCh V_CSR_INQ_7_7 Mode_7 [0-31] 32-bit offset for Mode 7

300h V_CSR_INQ_7_8 Mode_8 [0-31] 32-bit offset for Mode 8

To calculate the base address for an offset CSR:

1. Query the offset inquiry register.

2. Multiple the value by 4. (The value is a 32-bit offset.)

3. Remove the 0xF prefix from the result. (i.e., F70000h becomes 70000h)

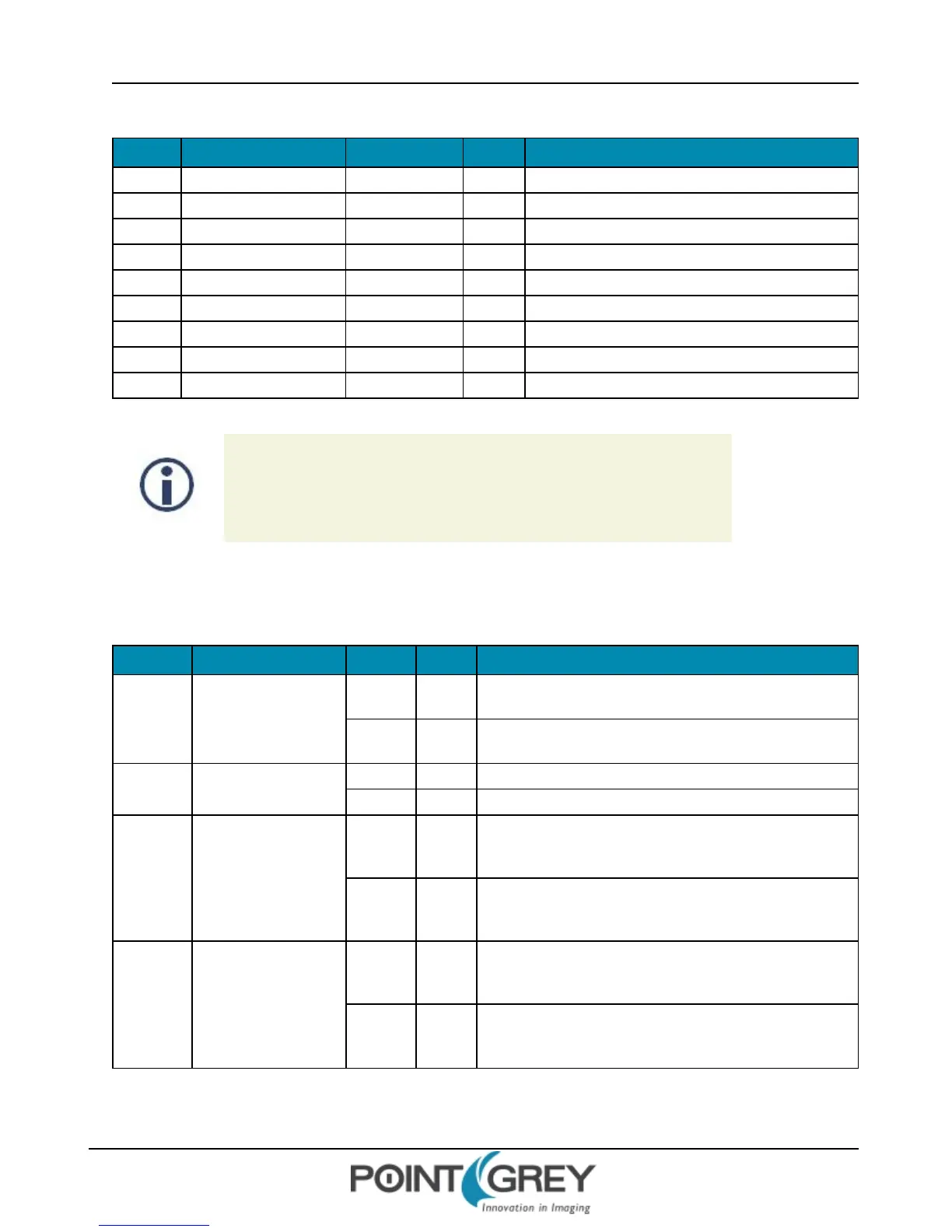

A.3.2.1 Image Size and Position

These registers are inquiry registers for maximum image size and unit size, and to determine an area of required data.

Address Name Field Bit Description

Base +

000h

MAX_IMAGE_SIZE_INQ

Hmax [0-15]

Maximum horizontal pixel number

Hmax = Hunit * n = Hposunit*n3 (n, n3 are integers)

Vmax [16-31]

Maximum vertical pixel number

Vmax = Vunit * m = Vposunit*m3 (m, m3 are integers)

Base +

004h

UNIT_SIZE_INQ

Hunit [0-15] Horizontal unit pixel number

Vunit [16-31] Vertical unit pixel number

Base +

04Ch

UNIT_POSITION_INQ

Hposunit [0-15]

Horizontal unit pixel number for position

If read value of Hposunit is 0, Hposunit = Hunit for IIDC 1.20

compatibility.

Vposunit [16-31]

Vertical unit number for position

If read value of Vposunit is 0, Vposunit = Vunit for IIDC1.20

compatibility.

Base +

008h

IMAGE_POSITION

Left [0-15]

Left position of requested image region (pixels)

Left = Hposunit * n1

Left + Width <= Hmax

Top [16-31]

Top position of requested image region (pixels)

Top = Vposunit * m1

Top + Height <= Vmax

Format:

Revised 9/27/2012

Copyright ©2011-2012 Point Grey Research Inc.

145

Loading...

Loading...