15. A/D Converter

puorG92/C61M

page 225

854fo7002,03.raM21.1.veR

2110-1010B90JER

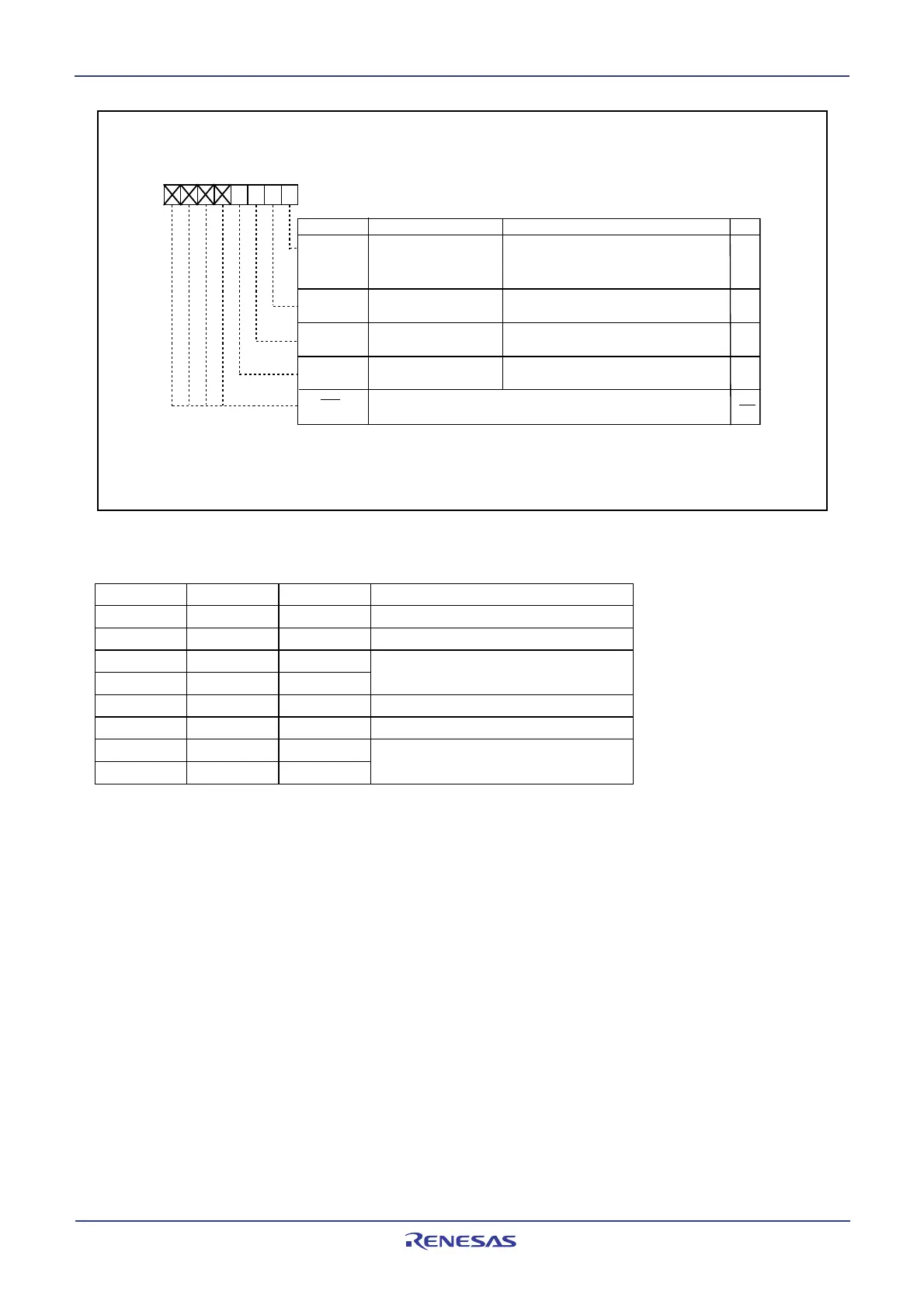

Figure 15.3 ADTRGCON Register

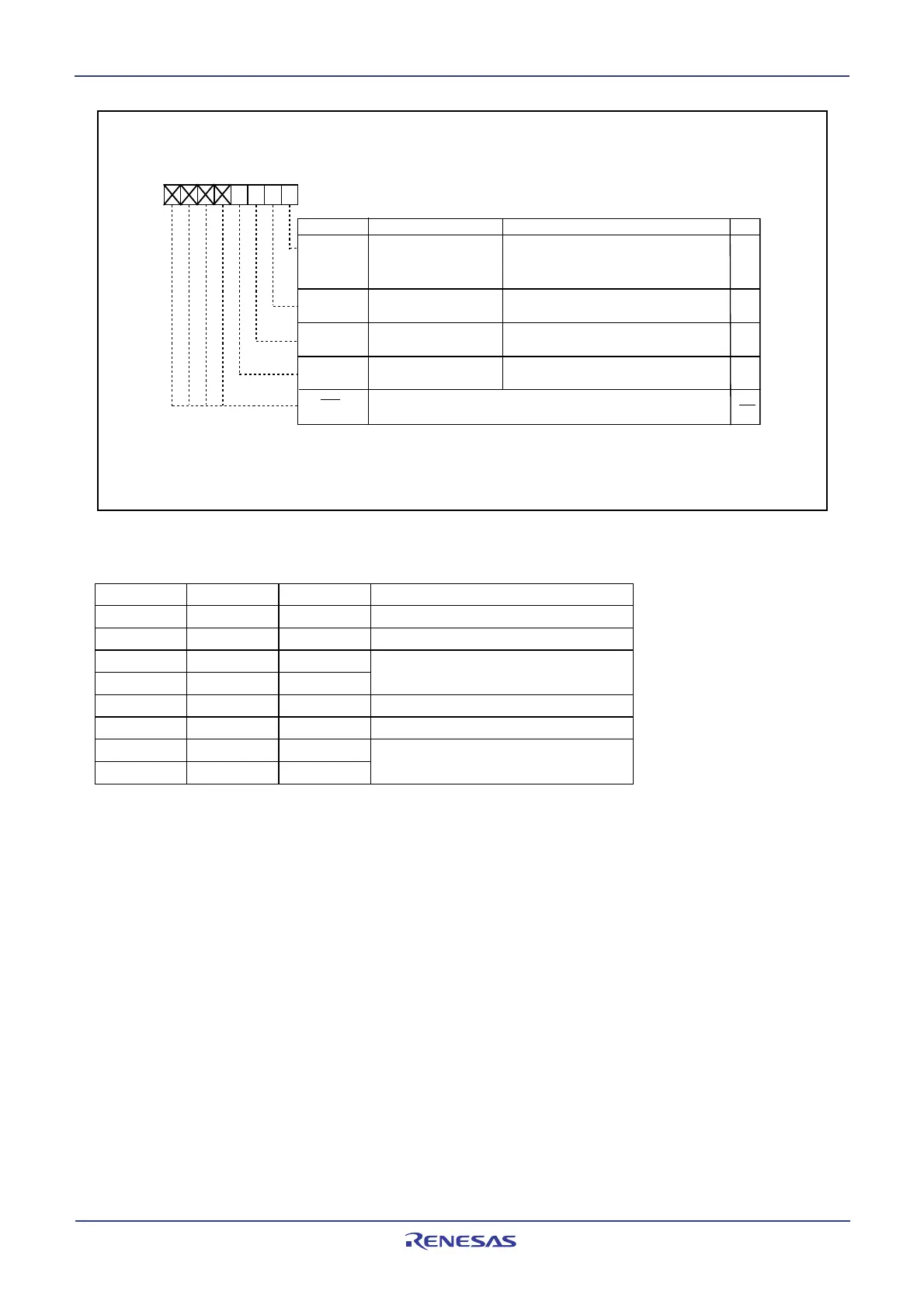

Table 15.2 A/D Conversion Frequency Select

2SKC1SKC0SKCDAØ

000 4ybdedividDAf

001 2ybdedividDAf

010

DAf

011

100 21ybdedividDAf

10 1 6ybdedividDAf

110

3ybdedividDAf

111

:ETON

.1 Ø ehtnitib0SKCehtfonoitanibmoC.zHM01rednuebtsumycneuqerfDA

ehtnitib2SKCehtdna,retsiger1NOCDAehtnitib1SKCeht,retsiger0NOCDA

stcelesretsiger2NOCDA.DAØ

A/D Trigger Control Register

(1, 2)

Symbol

Address

After Reset

ADTRGCON 03D216 0016

b7 b6 b5 b4 b3 b2 b1 b0

A/D Operation Mode

Select Bit 2

0 : Other than simultaneous sample sweep

mode or delayed trigger mode 0,1

1 : Simultaneous sample sweep mode or

delayed trigger mode 0,1

Bit Symbol

Bit Name Function

RW

SSE

A/D Operation Mode

Select Bit 3

HPTRG1

DTE

HPTRG0

RW

RW

RW

RW

Nothing is assigned. If necessary, set to 0.

When read, its content is 0

(b7-b4)

0 : Other than delayed trigger mode 0,1

1 : Delayed trigger mode 0,

1

NOTES:

1. If the ADTRGCON register is rewritten during A/D conversion, the conversion result will be undefined.

2. Set 00

16

in this register in one-shot mode, repeat mode, single sweep mode, repeat sweep mode 0 and repeat

sweep mode 1.

AN1 Trigger Select Bit

AN0 Trigger Select Bit

Function varies with each operation mode

Function varies with each operation mode

Loading...

Loading...