16. MULTI-MASTER I

2

C bus INTERFACE

puorG92/C61M

page 260

854fo7002,03.raM21.1.veR

2110-1010B90JER

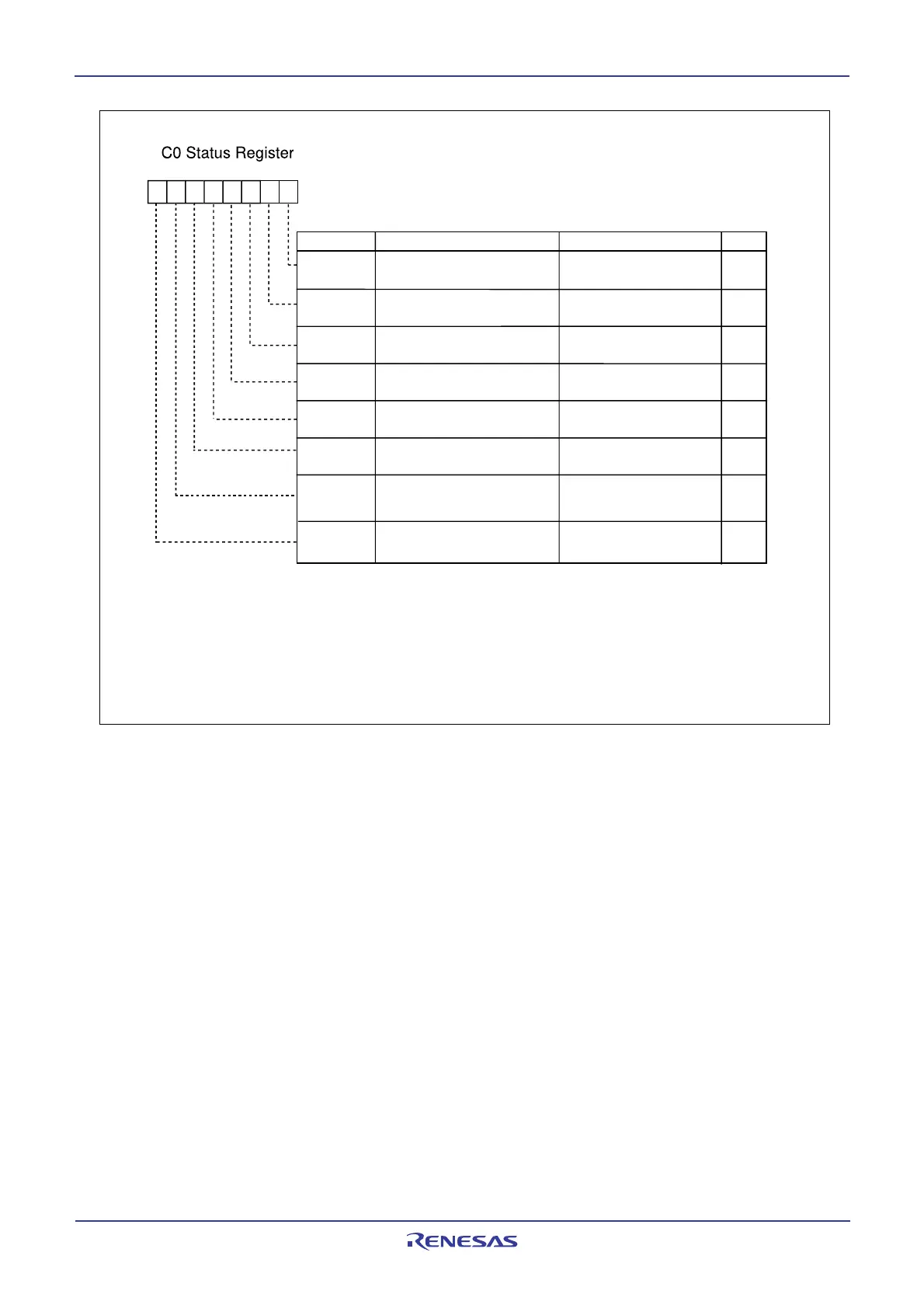

Figure 16.5 S10 Register

NOTES:

1. This bit is read only if it is used for the status check.

To write to this bit, refer to 16.9 START Condition Generation Method and 16.11 STOP Condition Generation

Method.

2. Read only. If necessary, set to 0.

3. To write to these bits, refer to 16.9 START Condition Generation Method and 16.11 STOP Condition

Generation Method.

0: Bus free

1: Bus busy

0: Interrupt request issued

1: No interrupt request issued

0: Not detected

1: Detected

0: No address matched

1: Address matched

0: No general call detected

1: General call detected

0: Last bit = 0

1: Last bit = 1

Communication mode select

bits 0

Bus busy flag

I C bus interface interrupt

request bit

2

Arbitration lost detection flag

Slave address comparison flag

General call detecting flag

Last receive bit

MST

TRX

BB

PIN

AL

AAS

ADR0

LRB

FunctionBit NameBit Symbol

0001000X

2

After Reset

02E8

16

AddressSymbol

S10

C0 Status Register

2

RW

0: Receive mode

1: Transmit mode

7

4

2b1b0

RO

(1)

RO

(1)

RO

(1)

RO

(2)

RO

(1)

RO

(2)

RW

(3)

RW

(3)

0: Slave mode

1: Master mode

Communication mode select

bit 1

Loading...

Loading...