16. MULTI-MASTER I

2

C bus INTERFACE

puorG92/C61M

page 259

854fo7002,03.raM21.1.veR

2110-1010B90JER

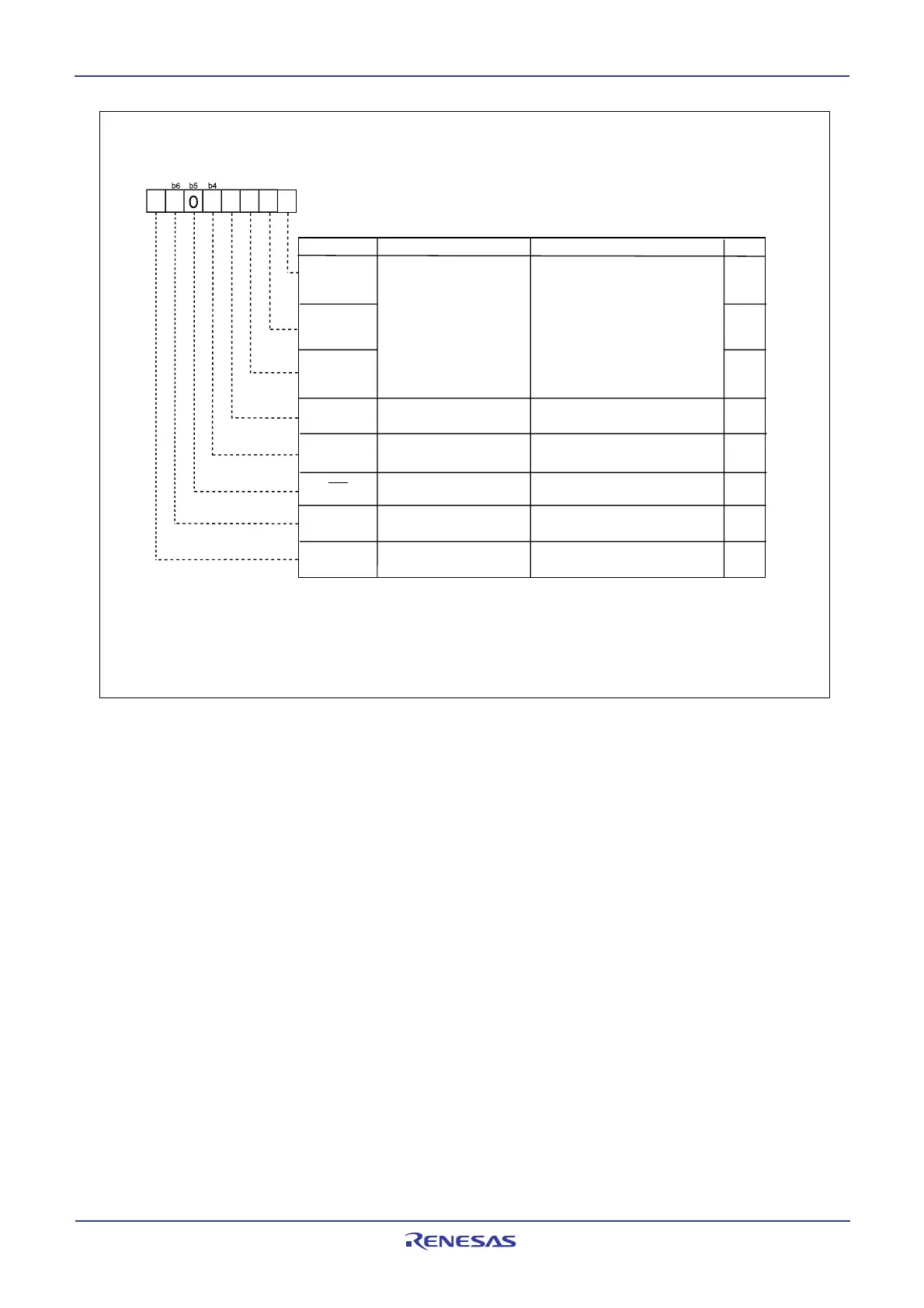

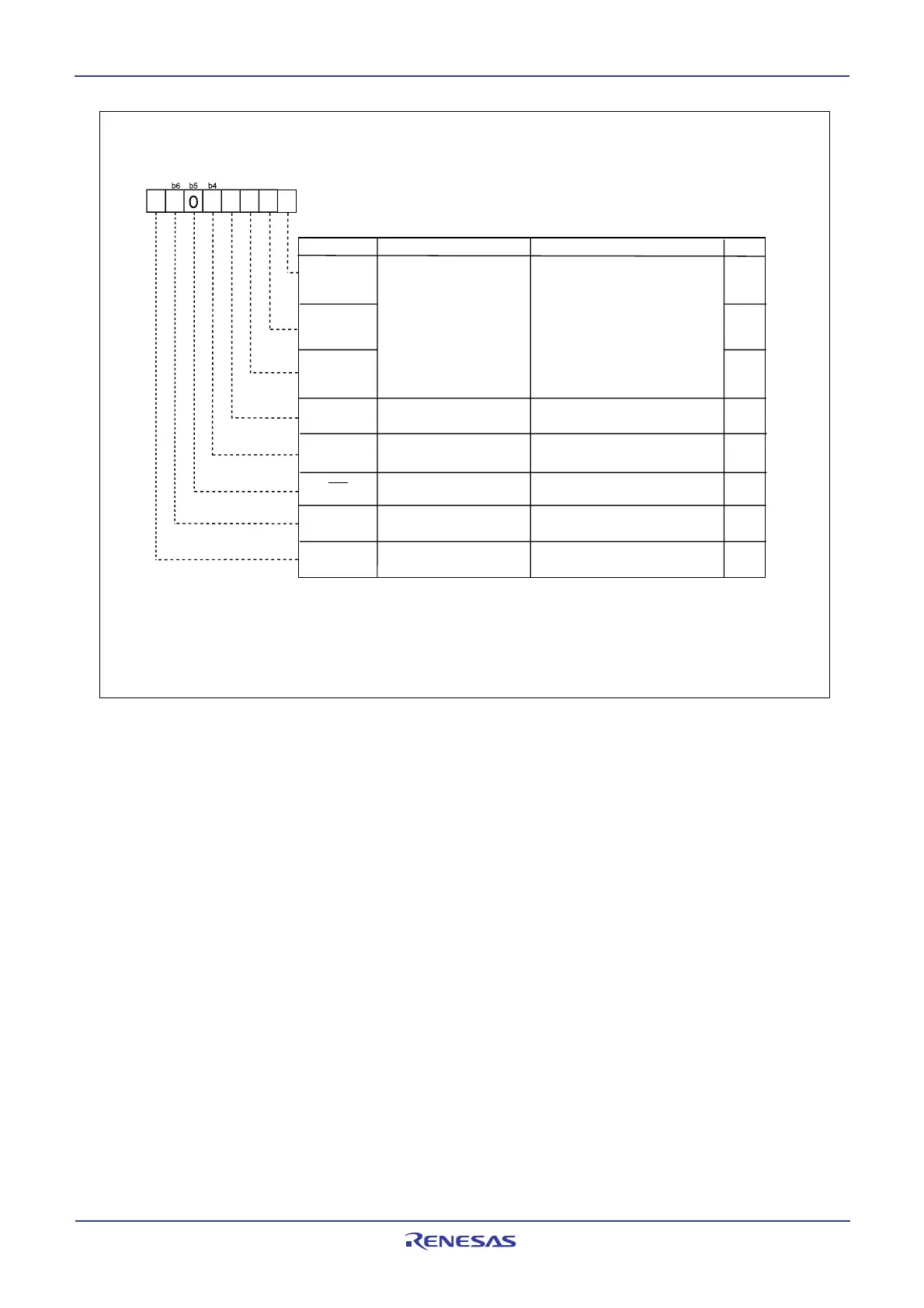

Figure 16.4 S1D0 Register

0: Disabled

1: Enabled

0: Addressing format

1: Free data format

Set to 0

0: Reset release (automatic)

1: Reset

NOTE:

1.In the following status, the bit counter is set to 000 automatically

•Start condition/stop condition are detected

•Immediately after the completion of 1-byte data transmit

•Immediately after the completion of 1-byte data receive

I

2

C bus interface pin

input level select bit

I

2

C bus interface

reset bit

Reserved bit

Data format select bit

I C bus interface

enable bit

2

Bit counter

(Number of transmit/receive

bits)

BC2

TISS

IHR

(b5)

ALS

ES0

BC1

BC0

FunctionBit NameBit Symbol

00

16

After Reset

02E3

16

AddressSymbol

S1D0

0

ontrol Re

ister 0I

2

7

2

1b0

(1)

RW

0: I

2

C bus input

1: SMBUS input

RW

RW

RW

RW

RW

RW

RW

RW

b2 b1 b0

0 0 0: 8

0 0 1: 7

0 1 0: 6

0 1 1: 5

1 0 0: 4

1 0 1: 3

1 1 0: 2

1 1 1: 1

Loading...

Loading...