16. MULTI-MASTER I

2

C bus INTERFACE

puorG92/C61M

page 285

854fo7002,03.raM21.1.veR

2110-1010B90JER

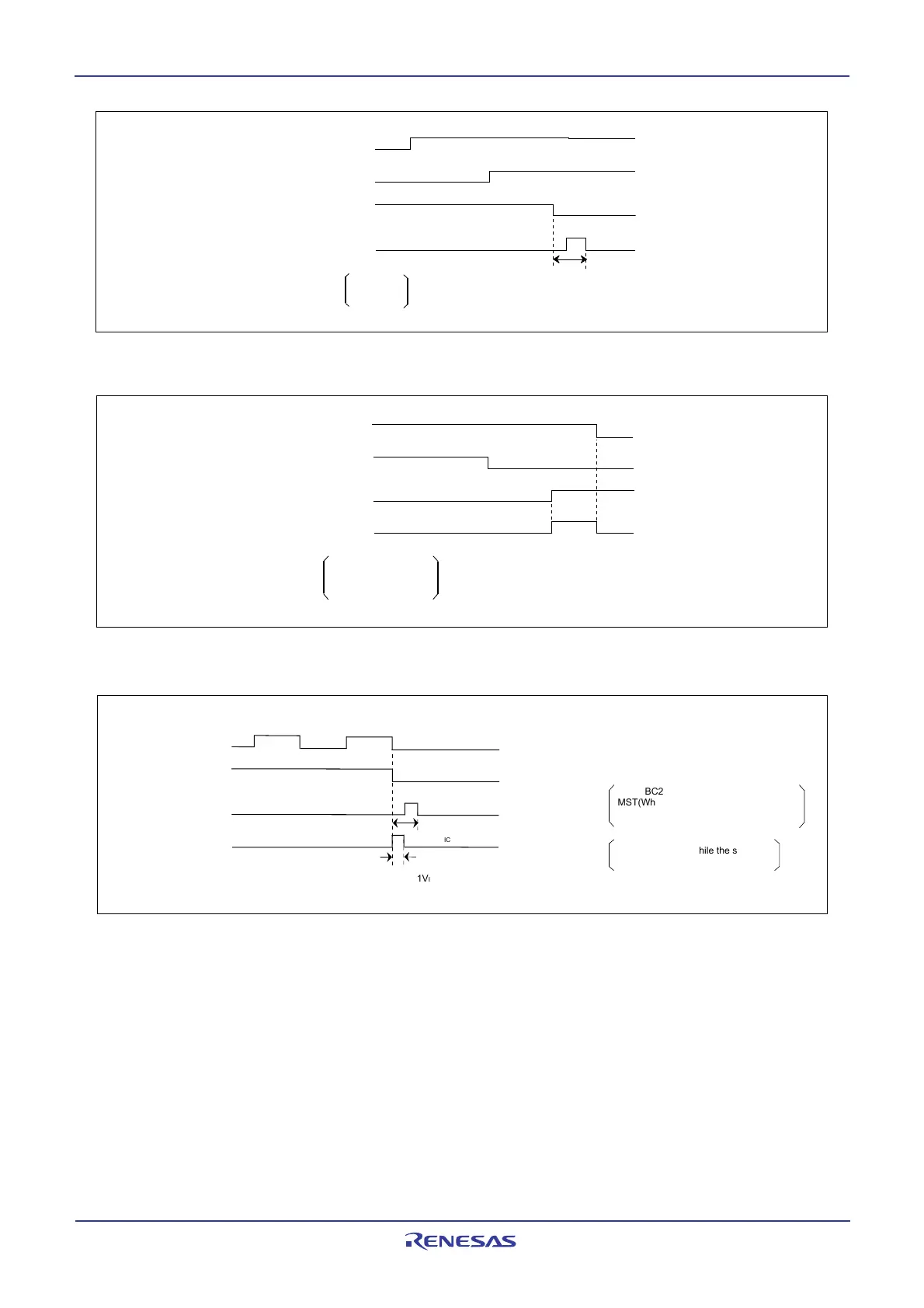

Figure 16.21 The bit reset timing (The STOP condition detection)

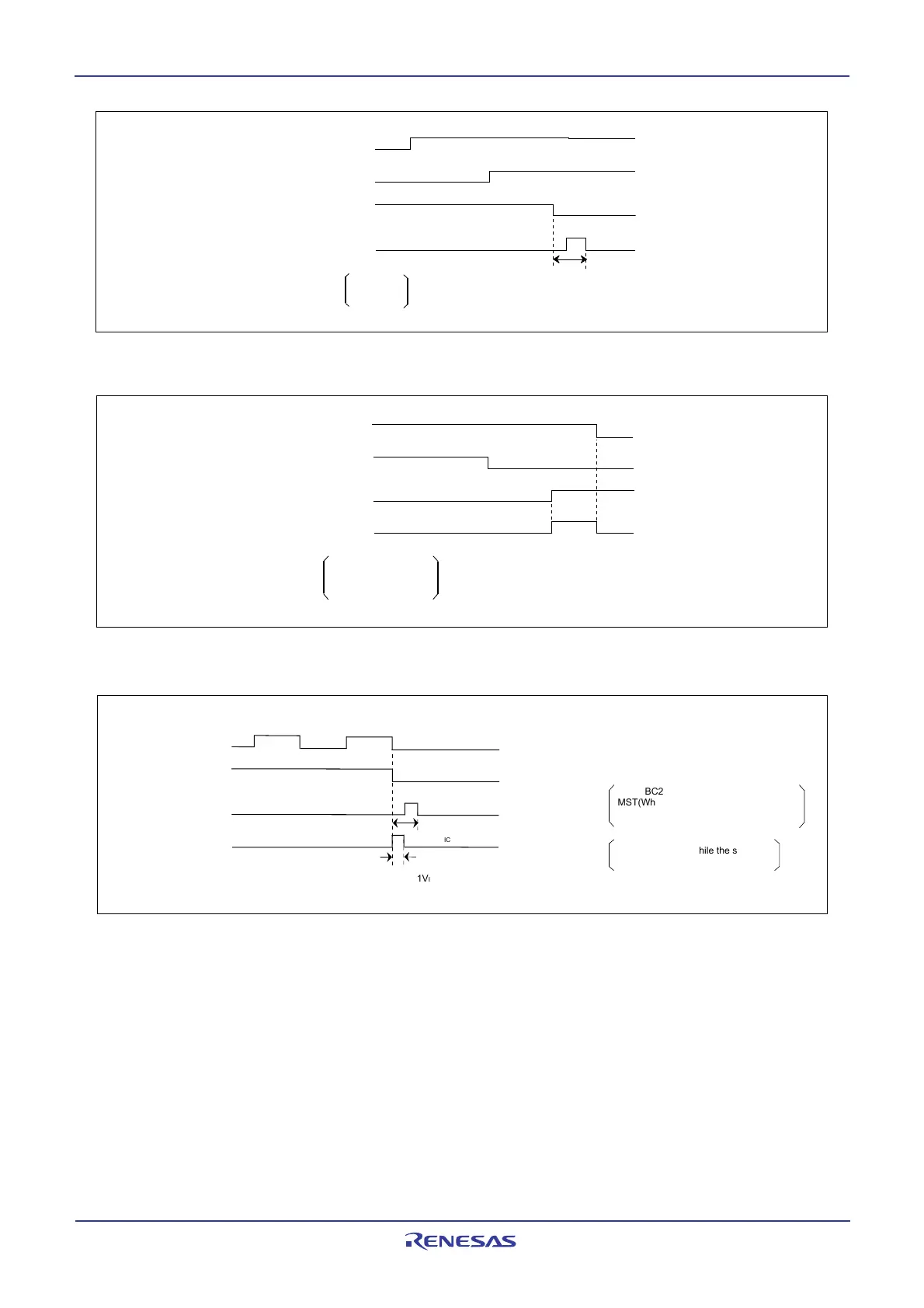

Figure 16.22 The bit reset timing (The START condition detection)

MST

TRX

BB flag

S

DA

S

CL

Bit reset signal

Related bits

1.5 V

IIC

cycle

BB flag

S

DA

SCL

Bit reset signal

BC2 - BC0

TRX (in slave mode)

Related bits

Figure 16.23 Bit set/reset timing ( at the completion of data transfer)

S

CL

Bit set signal

1V

IIC

c

cle

PIN bit

2V

IIC

cycle

Bit reset signal

BC0 - BC2

MST(When in arbitration lost)

TRX(When in NACK receive in slave

transmit mode)

The bits referring

to reset

TRX(ALS=0 meanwhile the slave

receive R/W bit = 1

The bits referring

to set

Loading...

Loading...