16. MULTI-MASTER I

2

C bus INTERFACE

puorG92/C61M

page 286

854fo7002,03.raM21.1.veR

2110-1010B90JER

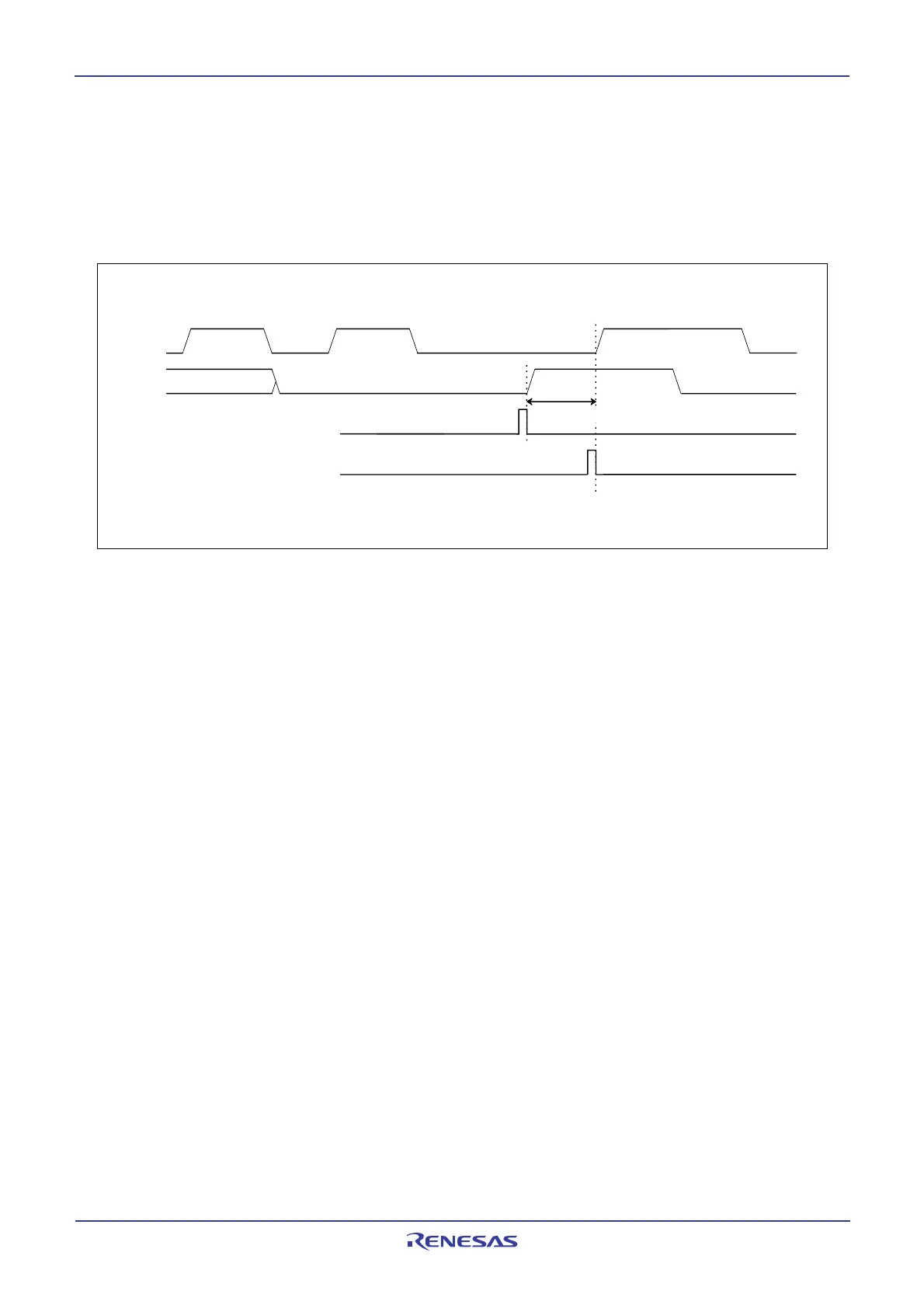

(2) Generation of RESTART condition

In order to generate a RESTART condition after 1-byte data transfer, write E016 to the S10 register,

enter START condition standby mode and leave the SDAMM open. Generate a START condition trigger

by setting the S00 register after inserting a sufficient software wait until the SDAMM outputs a high-level

("H") signal. Figure 16.24 shows the RESTART condition generation timing.

Figure 16.24 The time of generation of RESTART condition

8 clocks

ACK clock

S

CL

S10 writing signal

(START condition setting standby)

S

DA

S00 writing signal

(START condition triger generation)

Insert software wait

(3) Iimitation of CPU clock

When the CM07 bit in the CM0 register is set to 1 (subclock), each register of the I

2

C bus interface

circuit cannot be read or written. Read or write data when the CM07 bit is set to 0 (main clock, PLL

clock, or on-chip oscillator clock).

Loading...

Loading...