Overview of Interrupts

M30240 Group

Rev.1.00 Sep 24, 2003 Page 342 of 360

4.1.4.2 Interrupt Response Time

Interrupt response time is the period between the instant an interrupt occurs and the instant the first

instruction within the interrupt routine has been executed. This time includes the period from the oc-

currence of an interrupt to the completion of the instruction under execution at that moment (a) and

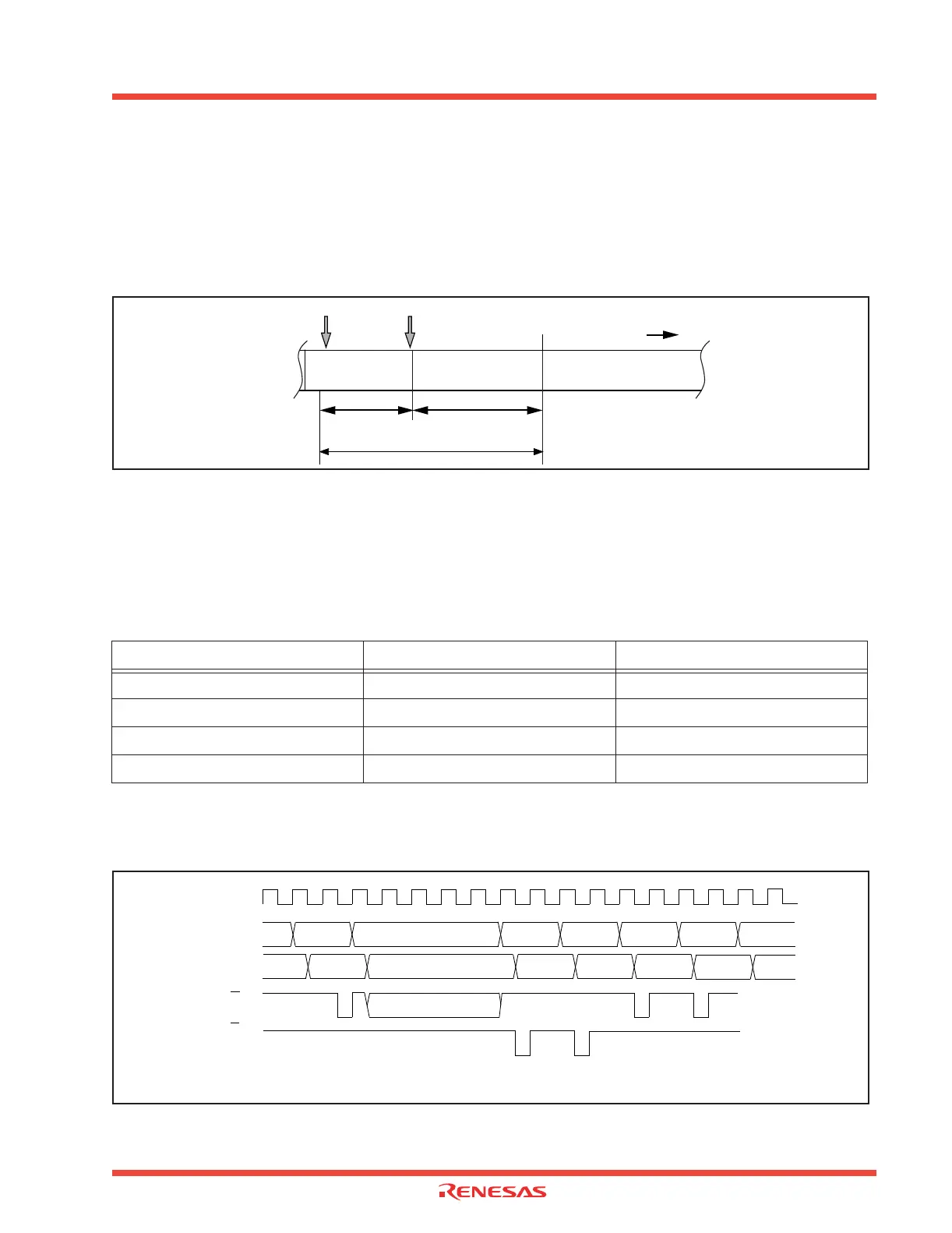

Figure 4.7 shows the interrupt response time. Figure 4.8 shows the

time required for executing and

interrupt sequence.

Figure 4.7: Interrupt response time

Time (a) is dependent on the instruction under execution. Thirty cycles is the maximum required for

the DIVX instruction (without wait).

Time (b) is as shown in Table 4.7 . Figure 4.5 shows the time required for executing the interrupt se-

quence.

Note 1: Add 2 cycles in the case of a DBC interrupt; add 1 cycle in the case of either an address match interrupt or a single

-step interrupt.

Note 2: Locate an interrupt vector address in an even address, if possible.

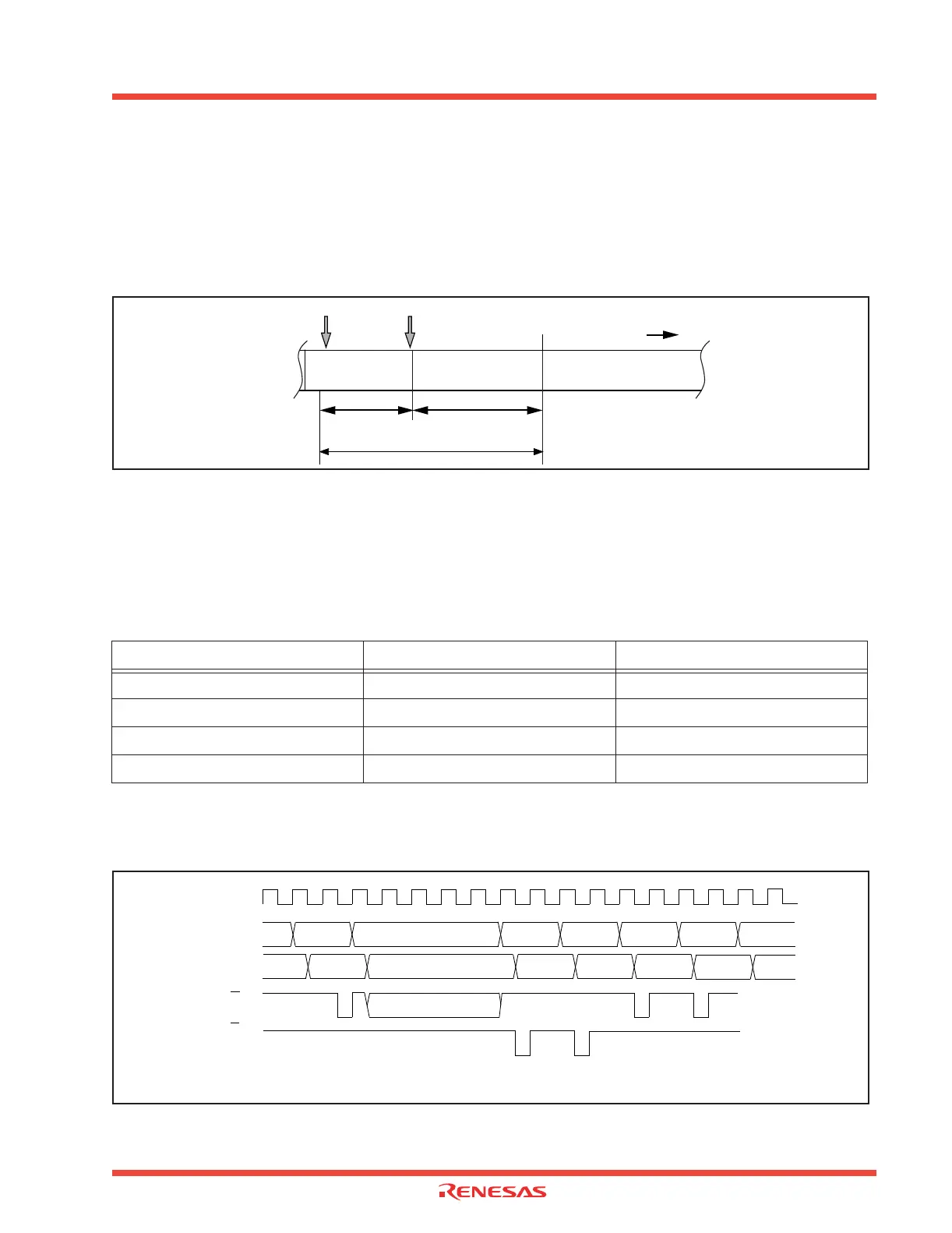

Figure 4.8: Time required for executing and interrupt sequence

Table 4.7: Time required for executing the interrupt sequence

Interrupt vector address Stack pointer (SP) value Cycle time, without wait

Even Even 18 cycles (Note 1)

Even Odd 18 cycles (Note 1)

Odd (Note 2) Even 19 cycles (Note 1)

Odd (note 2) Odd 20 cycles (Note 1)

Instruction Interrupt sequence

Instruction in

interrupt routine

Time

Interrupt response time

(a) (b)

Interrupt request acknowledgedInterrupt request generated

Indeterminate

12 3456789 101112 13 14 15 16 17 18

The indeterminate segment is dependent on the queue buffer.

If the queue buffer is ready to take an instruction, a read cycle occurs.

Indeterminate

SP-2

contents

SP-4

contents

vec

contents

vec+2

contents

Interrupt

information

Address

0000

Indeterminate SP-2 SP-4 vec vec+2

PC

Internal Clock Φ

Address bus

Data bus

W

R

Loading...

Loading...