Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 103

UG196 (v1.3) May 25, 2007

TX Buffering, Phase Alignment, and Buffer Bypass

R

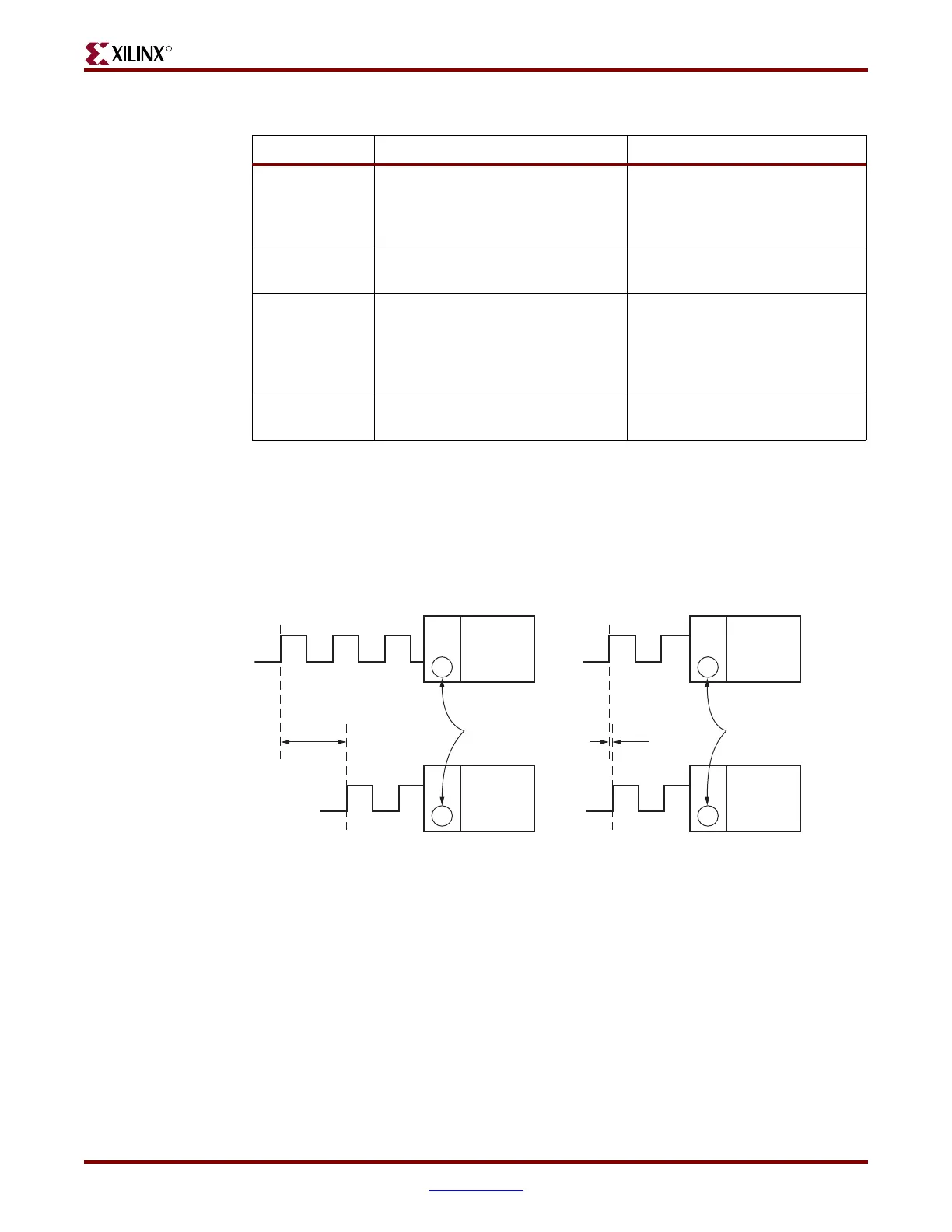

The TX phase-alignment circuit can also be used to minimize skew between GTP

transceivers. Figure 6-11 shows how the phase-alignment circuit can reduce lane skew by

aligning the PMACLK domains of multiple GTP transceivers to a common clock.

Figure 6-11 shows multiple lanes running before and after phase alignment to a common

clock. Before phase alignment, all PMACLKs have an arbitrary phase difference, but after

alignment, the only phase difference is the skew for the common clock, and all data is

transmitted simultaneously as long as the datapath latency is matched.

.

When oversampling is enabled (OVERSAMPLE_MODE = TRUE), the TX buffer is used for

bit interpolation and must always be active. See “Oversampling,” page 143 for more

information about built-in 5x oversampling.

Table 6-6: Buffering and Phase-Alignment Trade-Offs

TX Buffer TX Phase Alignment

Ease of Use

The TX buffer is used when possible.

It is robust and easy to operate.

Phase alignment requires extra

logic and additional constraints on

clock sources. TXOUTCLK cannot

be used.

Latency

If low latency is critical, the TX buffer

must be bypassed.

Phase alignment uses fewer

registers in the datapath.

Skew Reduction

TX buffers offer no benefit for skew

reduction.

The phase-alignment circuit can be

used to reduce the skew between

separate GTP transceivers. All

GTP transceivers involved must

use the same line rate.

Oversampling

The TX buffer is required for

oversampling.

Figure 6-11: Phase-Alignment Detail

Before

Phase Alignment

Parallel

Clocks Are

Independent

Skew

After

Phase Alignment

Parallel Clocks

Are Phase Aligned to

the Same Clock Edge

Reduced

Skew

GTP TX

GTP TXGTP TX

GTP TX

UG196_c6_11_080806

Loading...

Loading...