12

ABOV Semiconductor Co., Ltd.

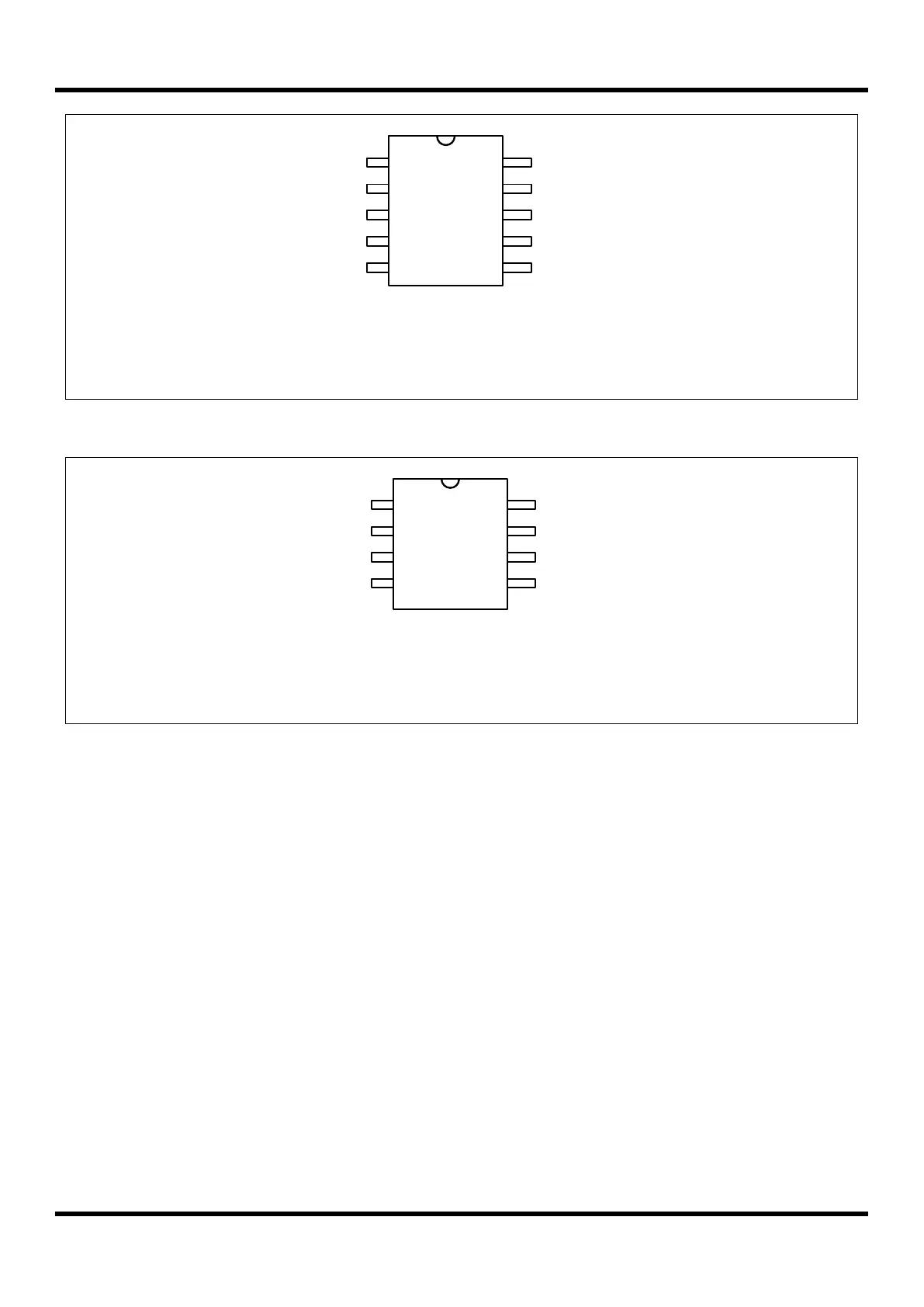

MC96F8104S

(10-SSOP)

1

2

3

4

8

7

10

9

VDD

P04/AN4/EINT10/EC2/SDA

P06/AN6/SS/XIN/SXIN

VSS

P05/AN5/AVREF/EC1/RESETB

P03/AN3/EINT12/T2O/PWM2O/SCL

P02/AN2/EINT11/T1O/PWM1O

P01/AN1/EINT1/RXD/MISO/DSCL

5

6

P07/AN7/SCK/XOUT/SXOUT P00/AN0/EINT0/TXD/MOSI/DSDA

NOTE)

1. On On-Chip Debugging, ISP uses P0[1:0] pin as DSCL, DSDA.

2. The P10-P17 and P20-P21 pins should be selected as a push-pull output or an input with pull-up resistor by

software control when the 10-pin package is used.

Figure 3.3 MC96F8104S 10SSOP Pin Assignment

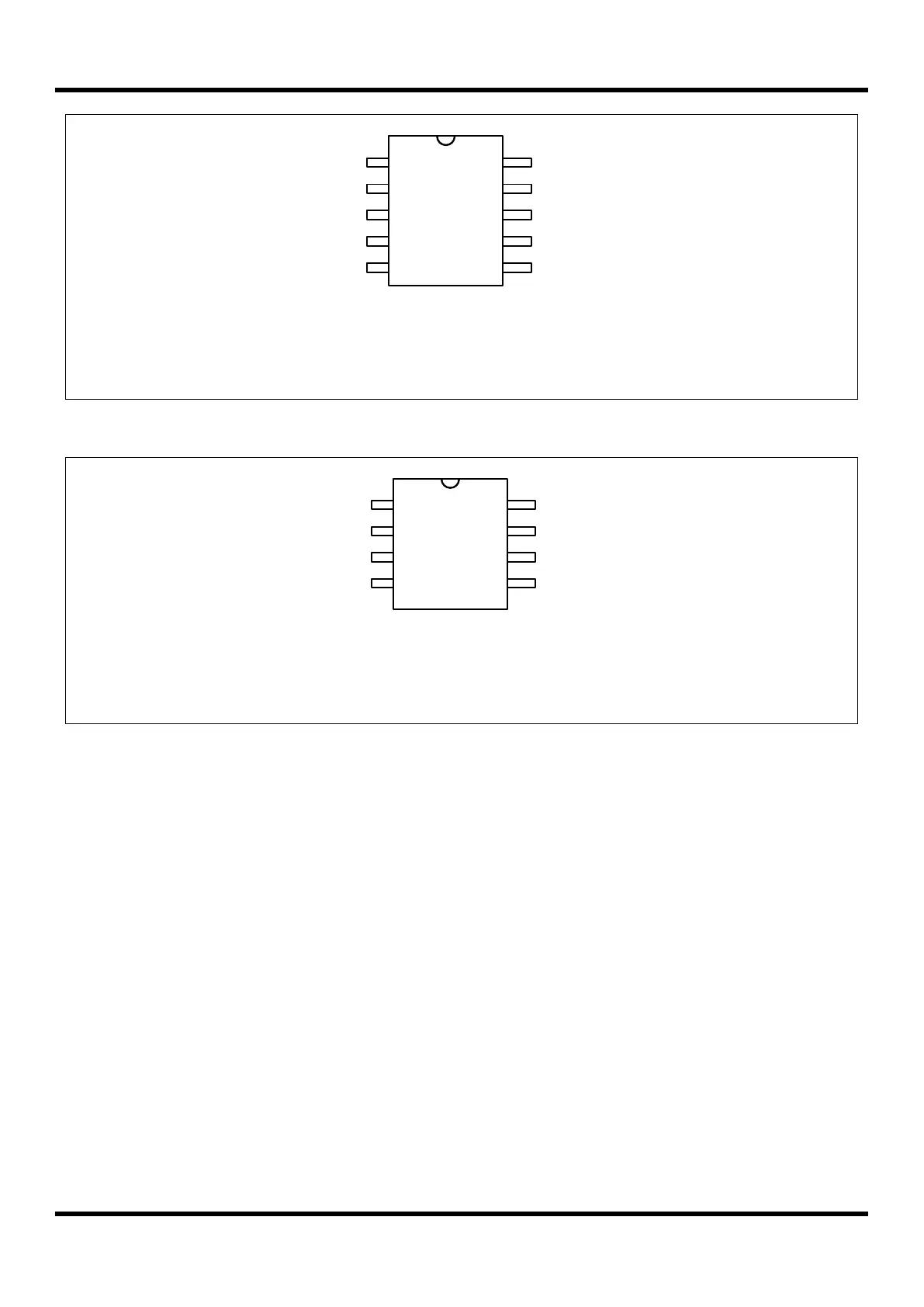

MC96F8104M

(8-SOP)

1

2

3

4

6

5

8

7

VDD

VSS

P02/AN2/EINT11/T1O/PWM1O

P01/AN1/EINT1/RXD/MISO/DSCL

P00/AN0/EINT0/TXD/MOSI/DSDA

P06/AN6/SS/XIN/SXIN

P07/AN7/SCK/XOUT/SXOUT

P05/AN5/AVREF/EC1/RESETB

NOTE)

1. On On-Chip Debugging, ISP uses P0[1:0] pin as DSCL, DSDA.

2. The P03-P04, P10-P17 and P20-P21 pins should be selected as a push-pull output or an input with pull-up

resistor by software control when the 8-pin package is used.

Figure 3.4 MC96F8104M 8SOP Pin Assignment

Loading...

Loading...