165

ABOV Semiconductor Co., Ltd.

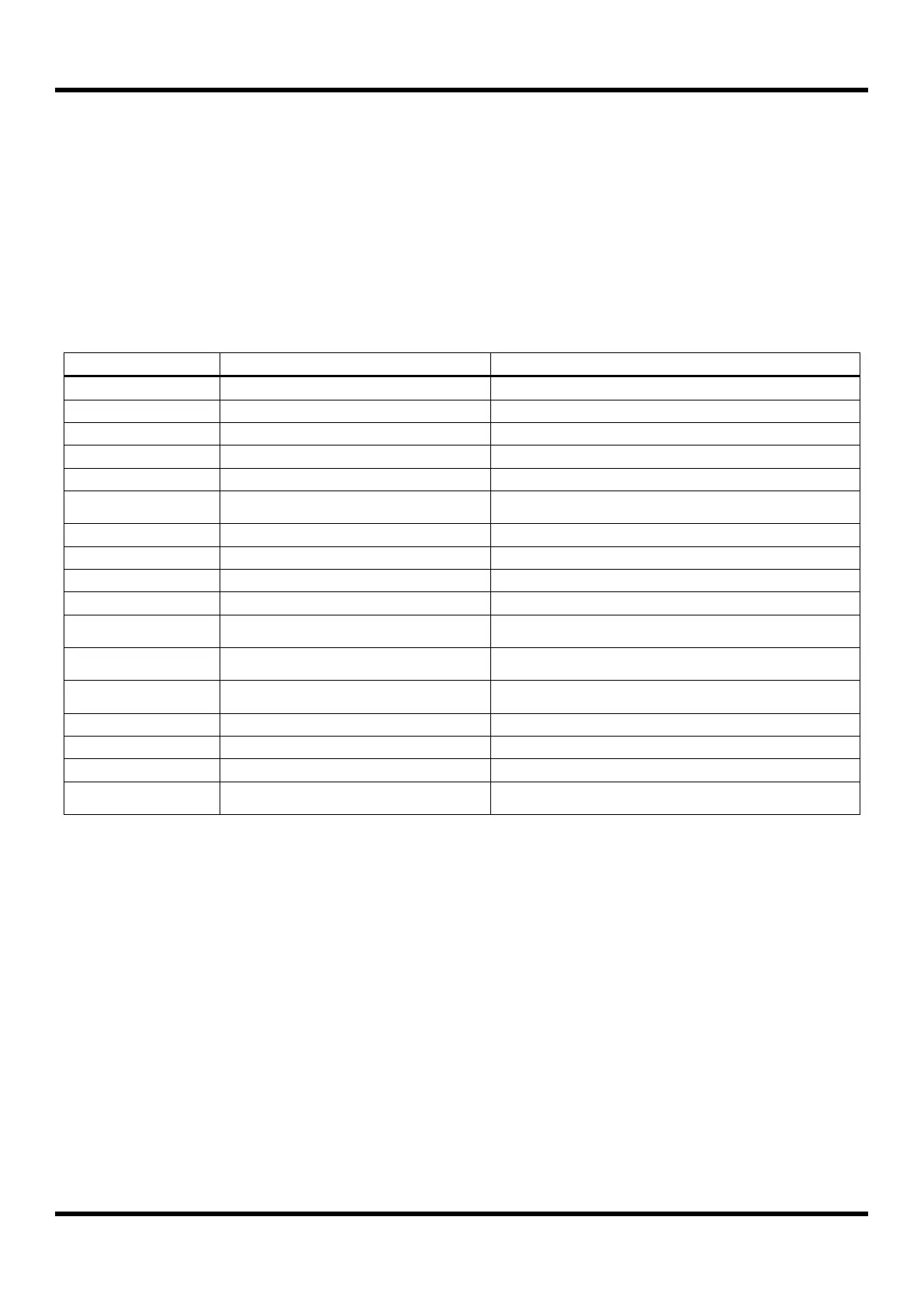

12 Power Down Operation

12.1 Overview

The MC96F8204 has two power-down modes to minimize the power consumption of the device. In power down mode,

power consumption is reduced considerably. The device provides three kinds of power saving functions, Main-IDLE,

Sub-IDLE and STOP mode. In three modes, program is stopped.

12.2 Peripheral Operation in IDLE/STOP Mode

ALL CPU Operation are Disable

ALL CPU Operation are Disable

Stop (Can be operated with WDTRC OSC)

Stop (Can be operated with sub clock)

Halted (Only when the Event Counter Mode is Enabled,

Timer operates Normally)

Only operate with external clock

Only operate with external clock

Stop when the system clock (fx) is fHFIRC or fLFIRC.

Can be operated with setting value

Can be operated with setting value

By RESET, Timer Interrupt (EC1, EC2),

External Interrupt, USART by RX, WT, WDT

Table 12.1 Peripheral Operation during Power Down Mode

Loading...

Loading...