168

ABOV Semiconductor Co., Ltd.

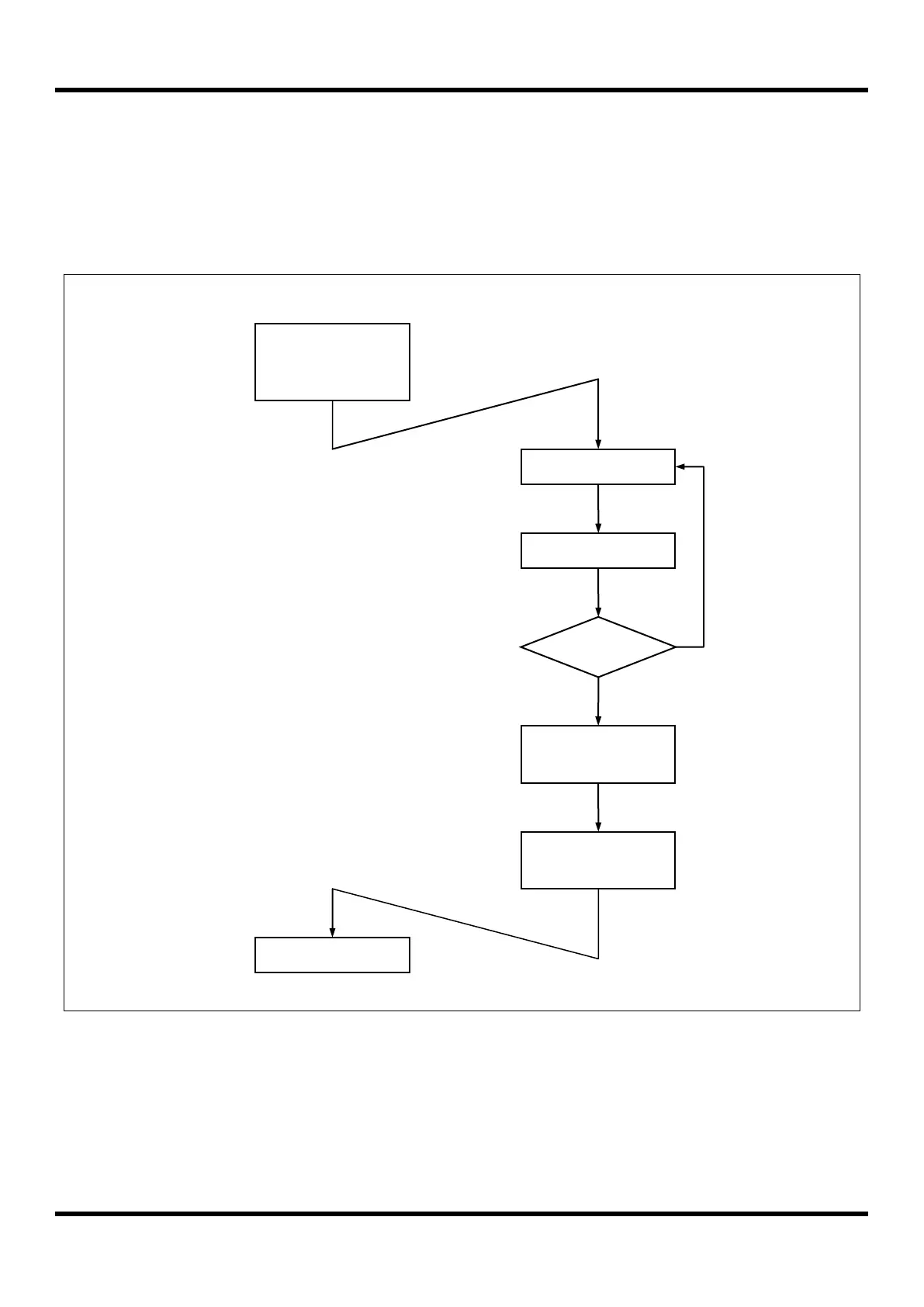

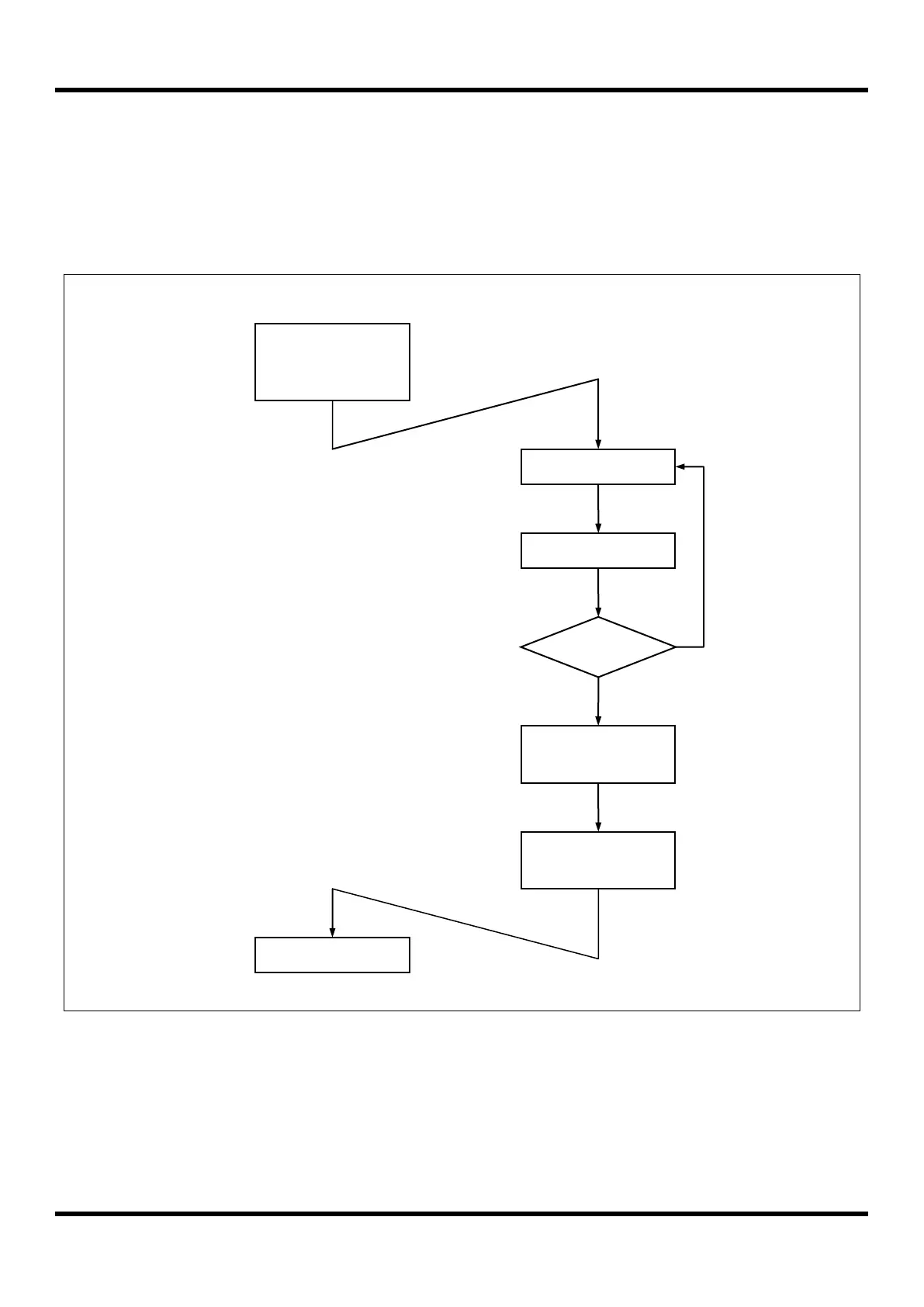

12.5 Release Operation of STOP Mode

After STOP mode is released, the operation begins according to content of related interrupt register just before STOP

mode start (Figure 12.3). If the global interrupt Enable Flag (IE.EA) is set to `1`, the STOP mode is released by the

interrupt which each interrupt enable flag = `1` and the CPU jumps to the relevant interrupt service routine. Even if the

IE.EA bit is cleared to ‘0’, the STOP mode is released by the interrupt of which the interrupt enable flag is set to ‘1’.

Figure 12.3 STOP Mode Release Flow

Interrupt Service

Routine

Corresponding Interrupt

Enable Bit(IE, IE1, IE2, IE3)

Loading...

Loading...