76

ABOV Semiconductor Co., Ltd.

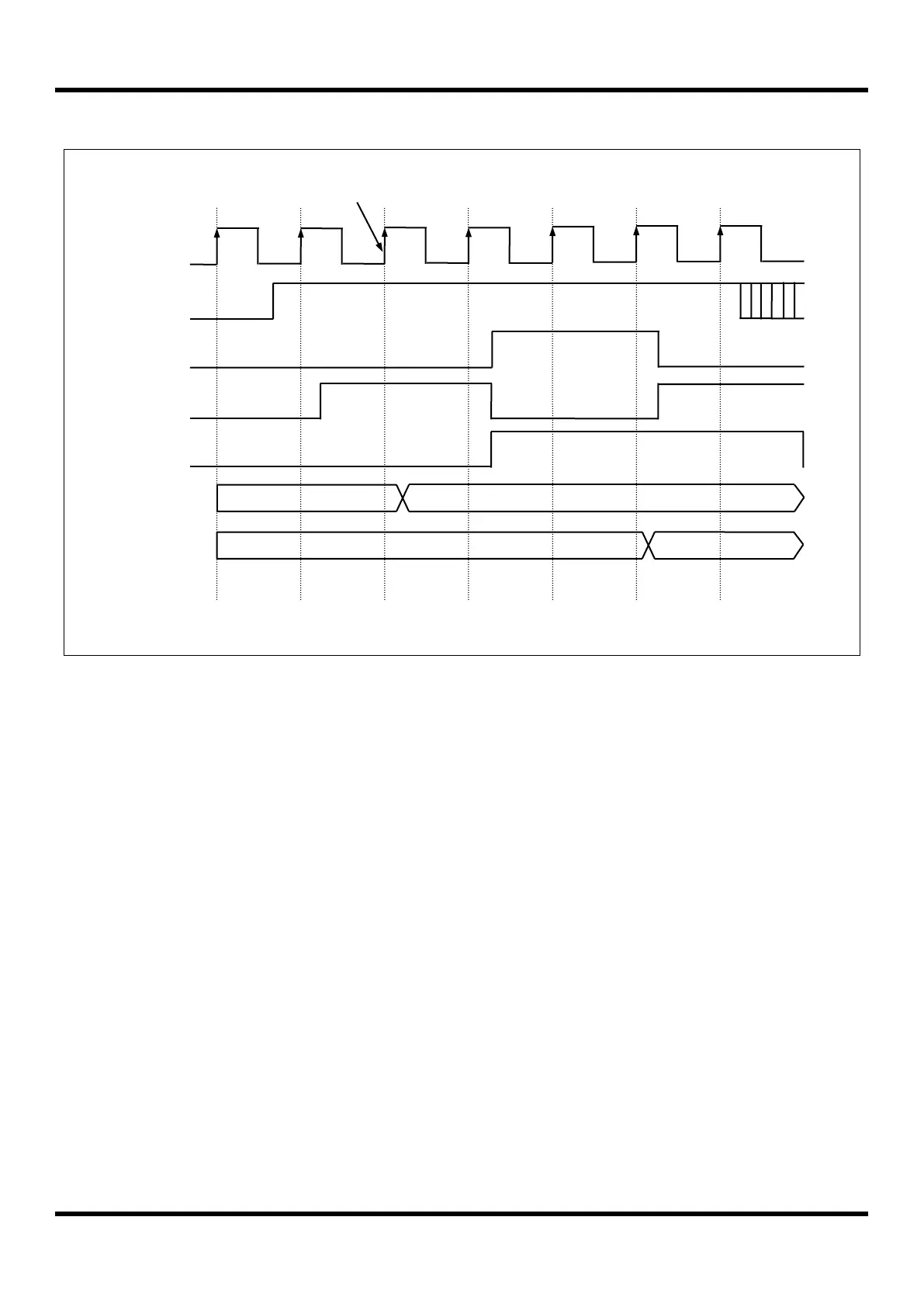

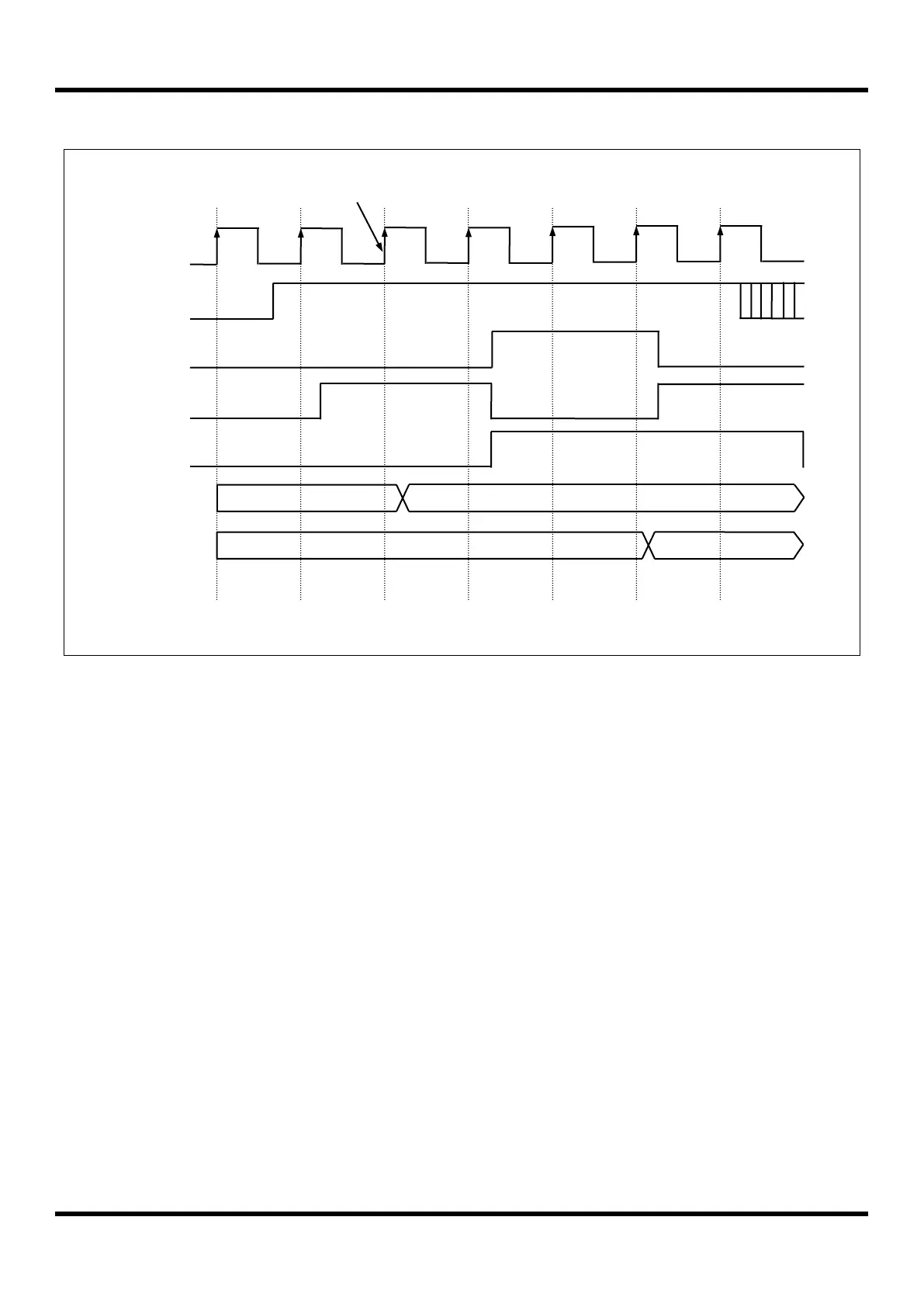

10.11 Interrupt Timing

Figure 10.10 Timing Chart of Interrupt Acceptance and Interrupt Return Instruction

Interrupt sources are sampled at the last cycle of a command. If an interrupt source is detected the lower 8-bit of

interrupt vector (INT_VEC) is decided. M8051W core makes interrupt acknowledge at the first cycle of a command,

and executes long call to jump to interrupt service routine.

NOTE)

1. command cycle CLPx: L=Last cycle, 1=1

st

cycle or 1

st

phase, 2=2

nd

cycle or 2

nd

phase

Loading...

Loading...