133

ABOV Semiconductor Co., Ltd.

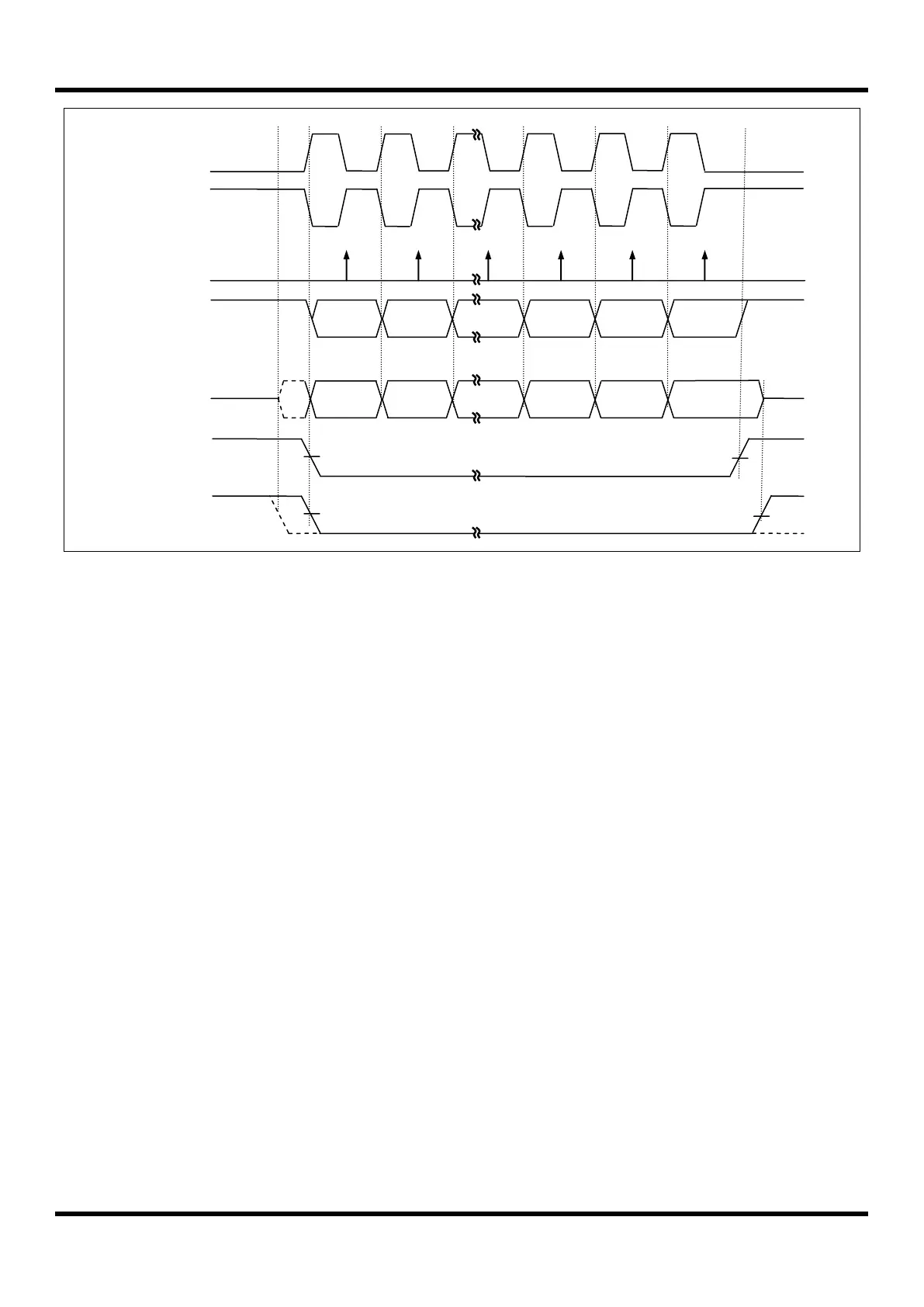

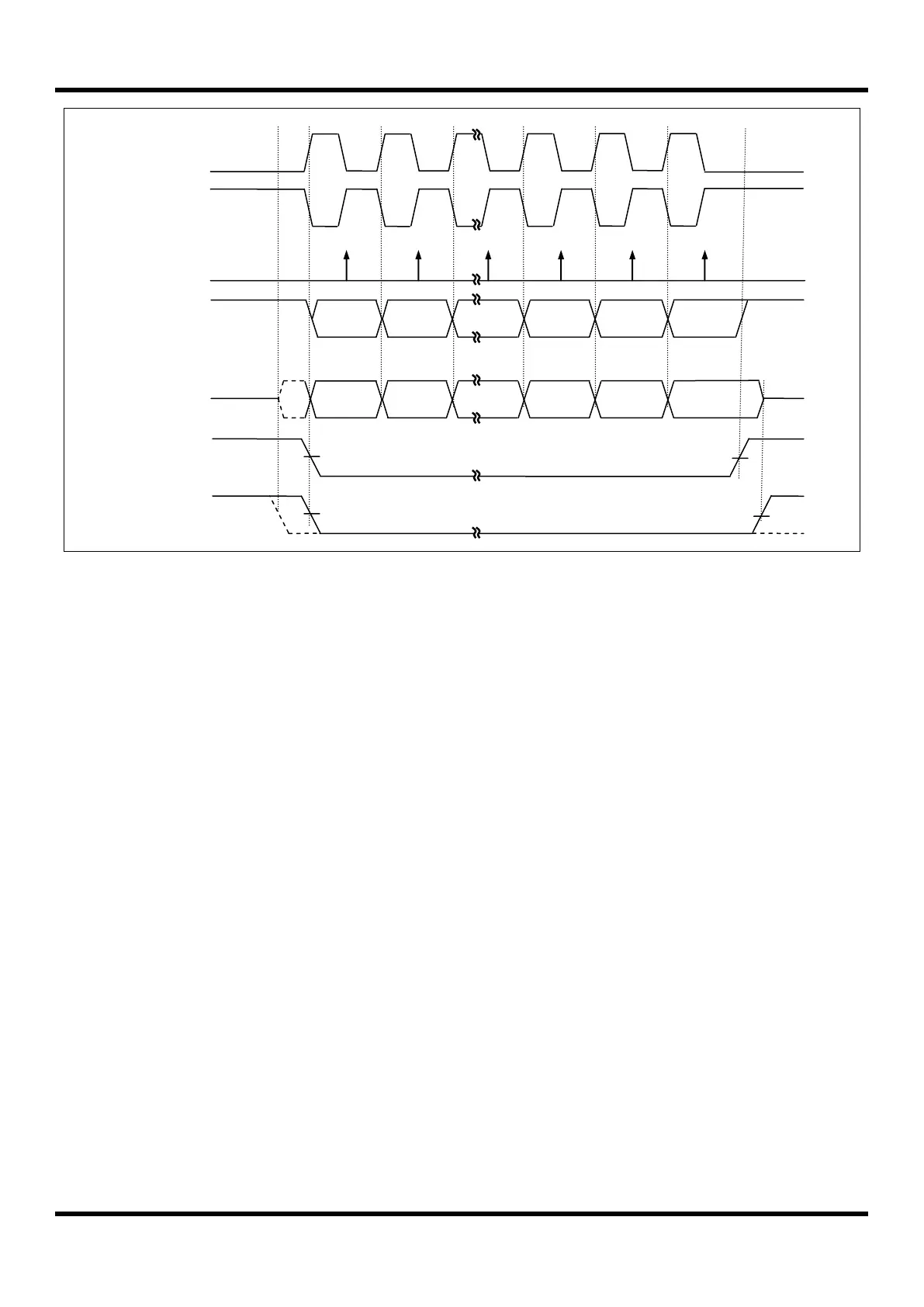

Figure 11.33 USART SPI Clock Formats when CPHA=1

When CPHA=1, the slave begins to drive its MISO output when SS goes active low, but the data is not defined until

the first SCK edge. The first SCK edge shifts the first bit of data from the shifter onto the MOSI output of the master

and the MISO output of the slave. The next SCK edge causes both the master and slave to sample the data bit value

on their MISO and MOSI inputs, respectively. At the third SCK edge, the USART shifts the second data bit value out to

the MOSI and MISO output of the master and slave respectively. When CPHA=1, the slave’s SS input is not required

to go to its inactive high level between transfers.

Because the SPI logic reuses the USART resources, SPI mode of operation is similar to that of synchronous or

asynchronous operation. An SPI transfer is initiated by checking for the USART Data Register Empty flag (DRE=1)

and then writing a byte of data to the USTDR Register. In master mode of operation, even if transmission is not

enabled (TXE=0), writing data to the USTDR register is necessary because the clock SCK is generated from

transmitter block.

Loading...

Loading...