BL702/704/706 Reference Manual

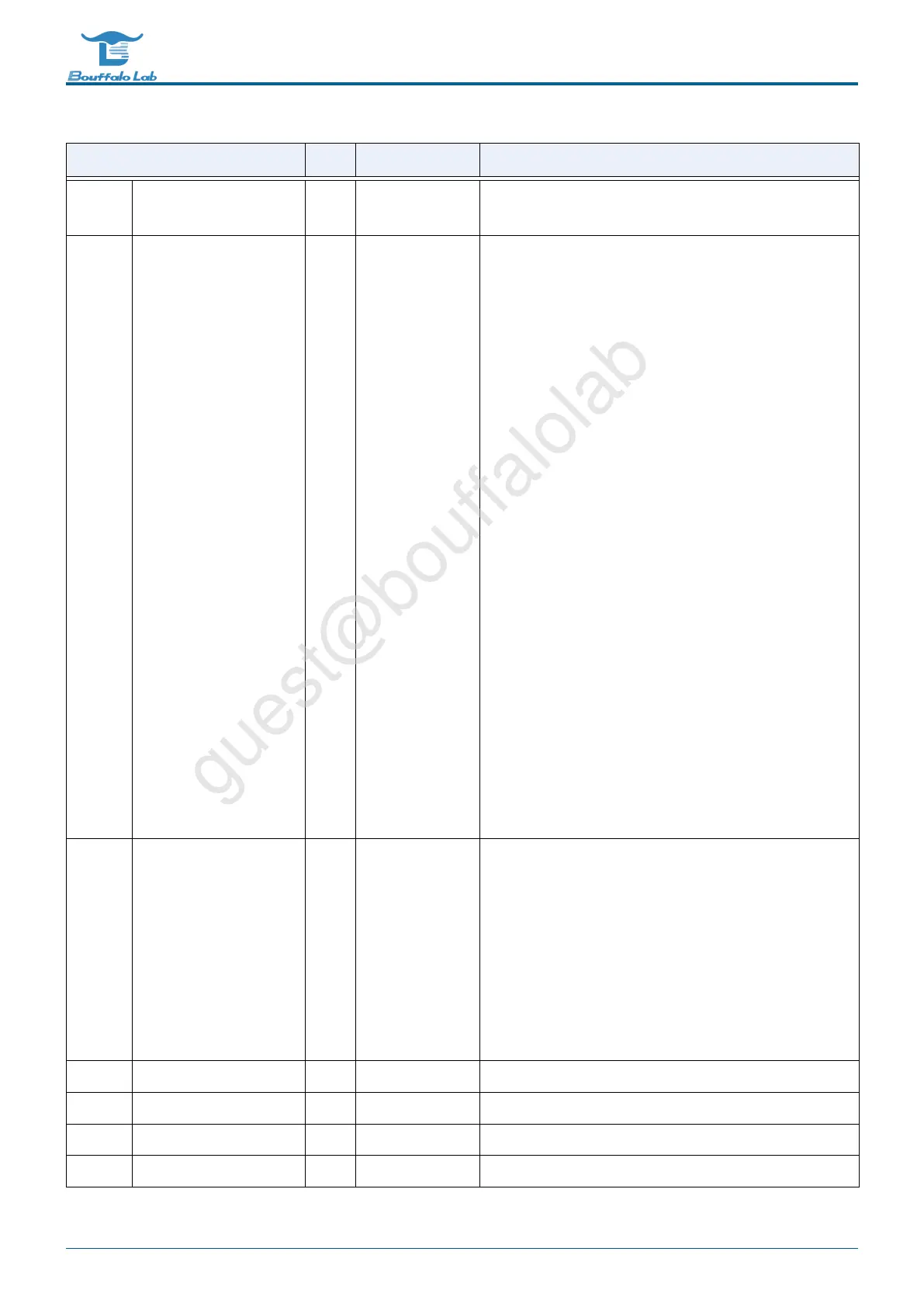

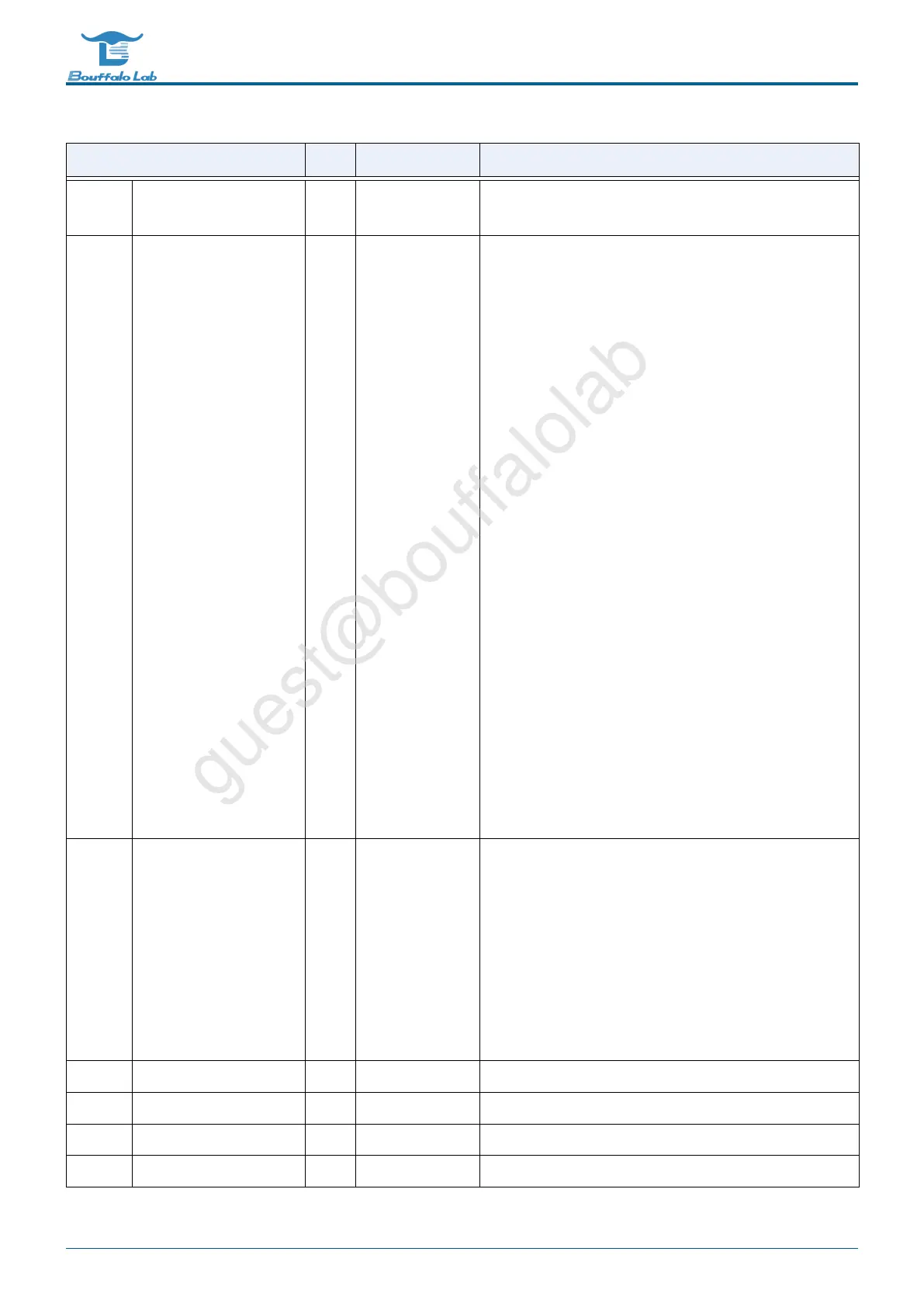

Bits

Name Type Reset Description

25 SCEN R/W 1’h0 select scan mode enable: 0: select gpadc_pos/neg_sel;1:

select : select gpadc_scan_pos_x and gpadc_scan_neg_x

24:21 SCLEN R/W 4’h0 select scan mode length

4’b0000 : select gpadc_scan_pos_0 and gpadc_scan_-

neg_0

4’b0001 : select gpadc_scan_pos_1 and gpadc_scan_-

neg_1

4’b0010 : select gpadc_scan_pos_2 and gpadc_scan_-

neg_2

4’b0011 : select gpadc_scan_pos_3 and gpadc_scan_-

neg_3

4’b0100 : select gpadc_scan_pos_4 and gpadc_scan_-

neg_4

4’b0101 : select gpadc_scan_pos_5 and gpadc_scan_-

neg_5

4’b0110 : select gpadc_scan_pos_6 and gpadc_scan_-

neg_6

4’b0111 : select gpadc_scan_pos_7 and gpadc_scan_-

neg_7

4’b1000 : select gpadc_scan_pos_8 and gpadc_scan_-

neg_8

4’b1001 : select gpadc_scan_pos_9 and gpadc_scan_-

neg_9

4’b1010 : select gpadc_scan_pos_10 and gpadc_scan_-

neg_10

4’b1011 : select gpadc_scan_pos_11 and gpadc_scan_-

neg_11

20:18 CLKDVRT R/W 3’h3 analog 32M clock division ratio

3’b000: div=1

3’b001: div=4

3’b010: div=8

3’b011: div=12

3’b100: div=16

3’b101: div=20

3’b110: div=24

3’b111: div=32

17 ALCLKINV R/W 1’b0 analog clock 2M inverted

16:11 RSVD

10 LDEN R/W 1’b0 Low power supply detected enable

9 HYSTSEL R/W 1’b0 pga vcm hystersis select when vcm_sel_en is enabled

BL702/704/706 Reference Manual 104/ 375

@2021 Bouffalo Lab

Loading...

Loading...