BL702/704/706 Reference Manual

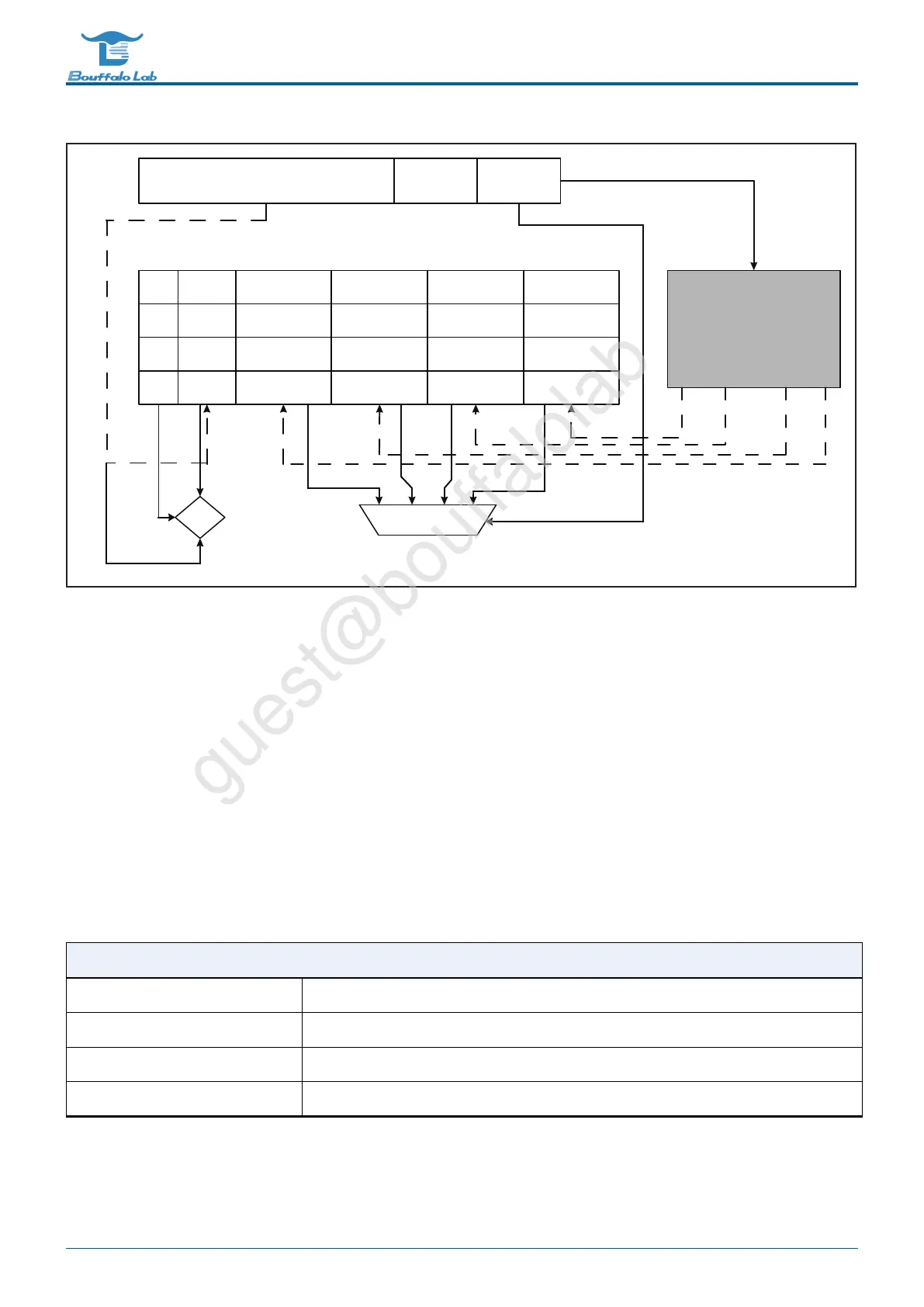

tag index offset

valid tag Word 3 Word 2 Word 1 Word 0

RAM

HIT

Fig. 7.2: Cache architecture

Each set of associative mapping caches contains two parts, the first is a tag, which contains the valid value and the

address mapping relationship. The second part is data storage. When the processor accesses the cache, the cache

processor compares the relationship between the address and the tag. When the address comparison is successful,

the representative can directly get data from the cache. Conversely, the cache processor will capture related data

through the AHB Master and put the data into the cache and respond to the processor’s data.

When most of the data can be successfully compared in the tag, the waiting time of the processor can be greatly

reduced, and the use efficiency can be increased.

7.4 Register description

Name

Description

l1c_config L1C configuration

hit_cnt_lsb Low 32-bit hit couter

hit_cnt_msb High 32-bit hit counter

miss_cnt Miss counter

BL702/704/706 Reference Manual 160/ 375

@2021 Bouffalo Lab

Loading...

Loading...