BL702/704/706 Reference Manual

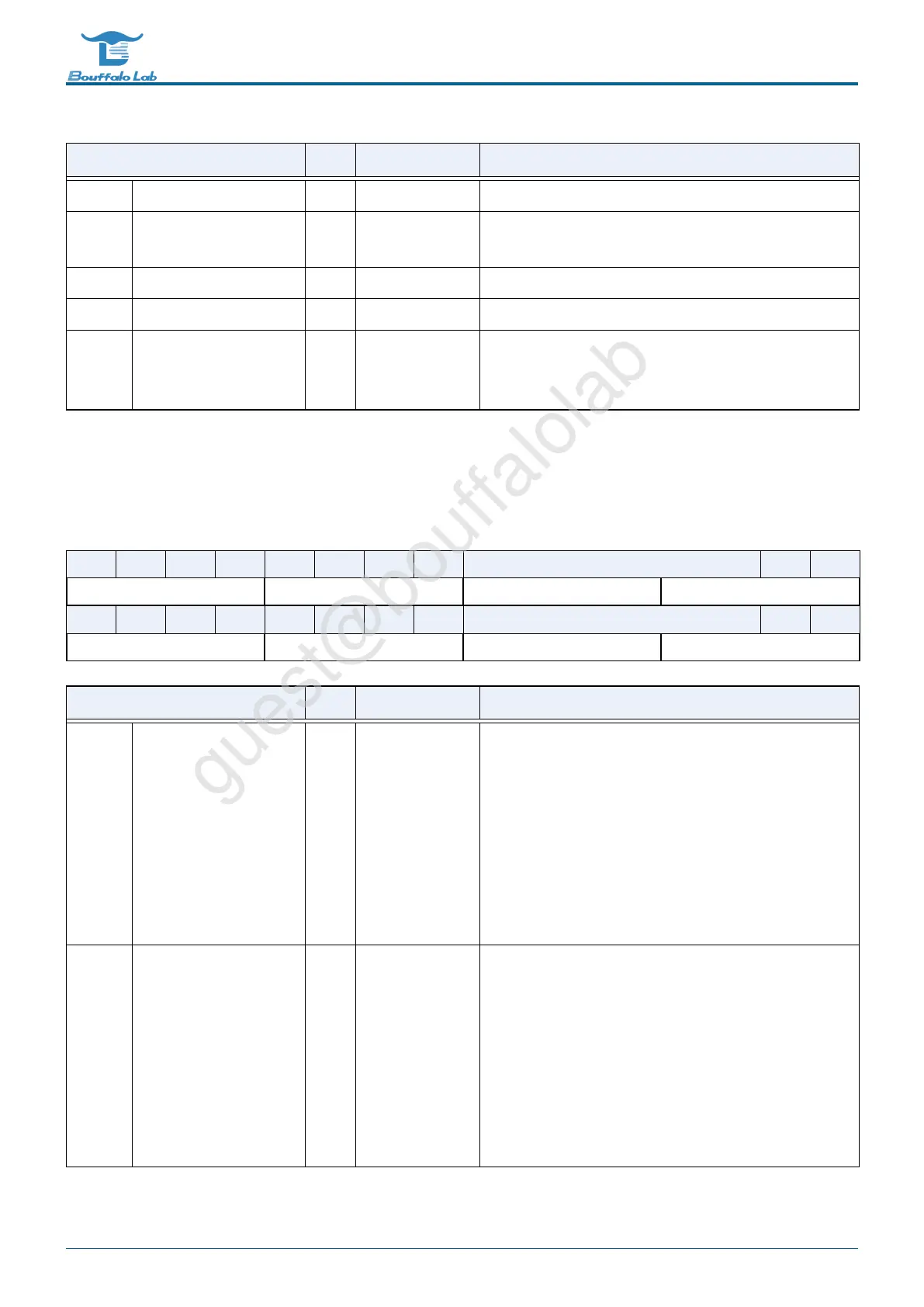

Bits

Name Type Reset Description

15:14 RSVD

13 32KCOMP R/W 0 Compensation => Duty of dig_32k_out = dig_32k_div :

(dig_32k_div+1)

12 32KEN R/W 1 Enable dig_32k_out

11 RSVD

10:0 32KDIV R/W 11’d1000 (PLL 32MHz or xclk) / dig_32k_div

Ex: Set 750 for 24MHz ; Set 1000 for 32MHz ; Set 1200 for

38.4MHz ; Set 1250 for 40MHz

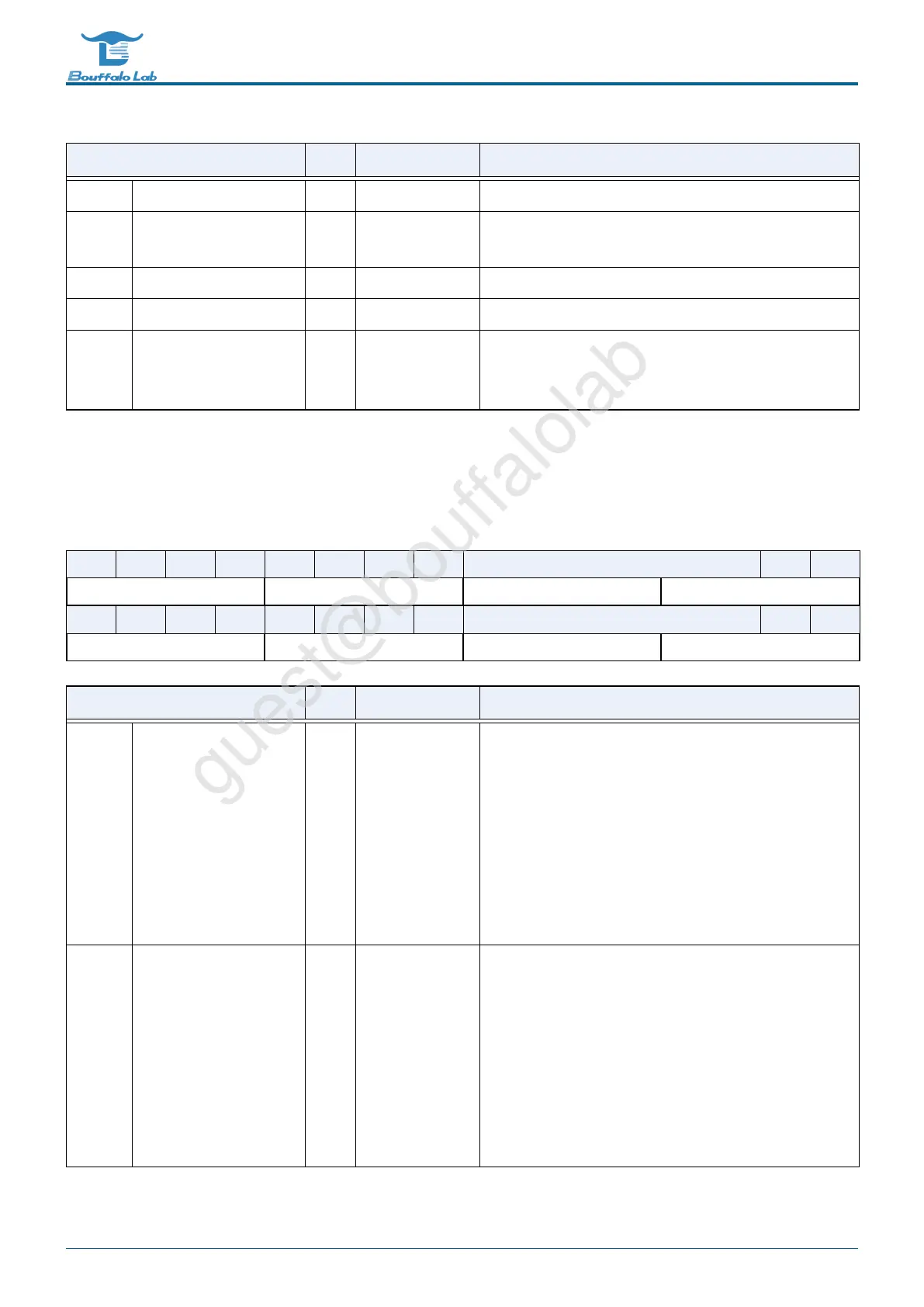

3.3.17 UART_SIG_SEL_0

Address:0x400000c0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

SIG7SEL SIG6SEL SIG5SEL SIG4SEL

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SIG3SEL SIG2SEL SIG1SEL SIG0SEL

Bits

Name Type Reset Description

31:28 SIG7SEL R/W 4’d7 UART Signal7 Select :

0 : UART0_RTS

1 : UART0_CTS

2 : UART0_TXD

3 : UART0_RXD

4 : UART1_RTS

5 : UART1_CTS

6 : UART1_TXD

7 : UART1_RXD

27:24 SIG6SEL R/W 4’d6 UART Signal6 Select :

0 : UART0_RTS

1 : UART0_CTS

2 : UART0_TXD

3 : UART0_RXD

4 : UART1_RTS

5 : UART1_CTS

6 : UART1_TXD

7 : UART1_RXD

BL702/704/706 Reference Manual 51/ 375

@2021 Bouffalo Lab

Loading...

Loading...