BL702/704/706 Reference Manual

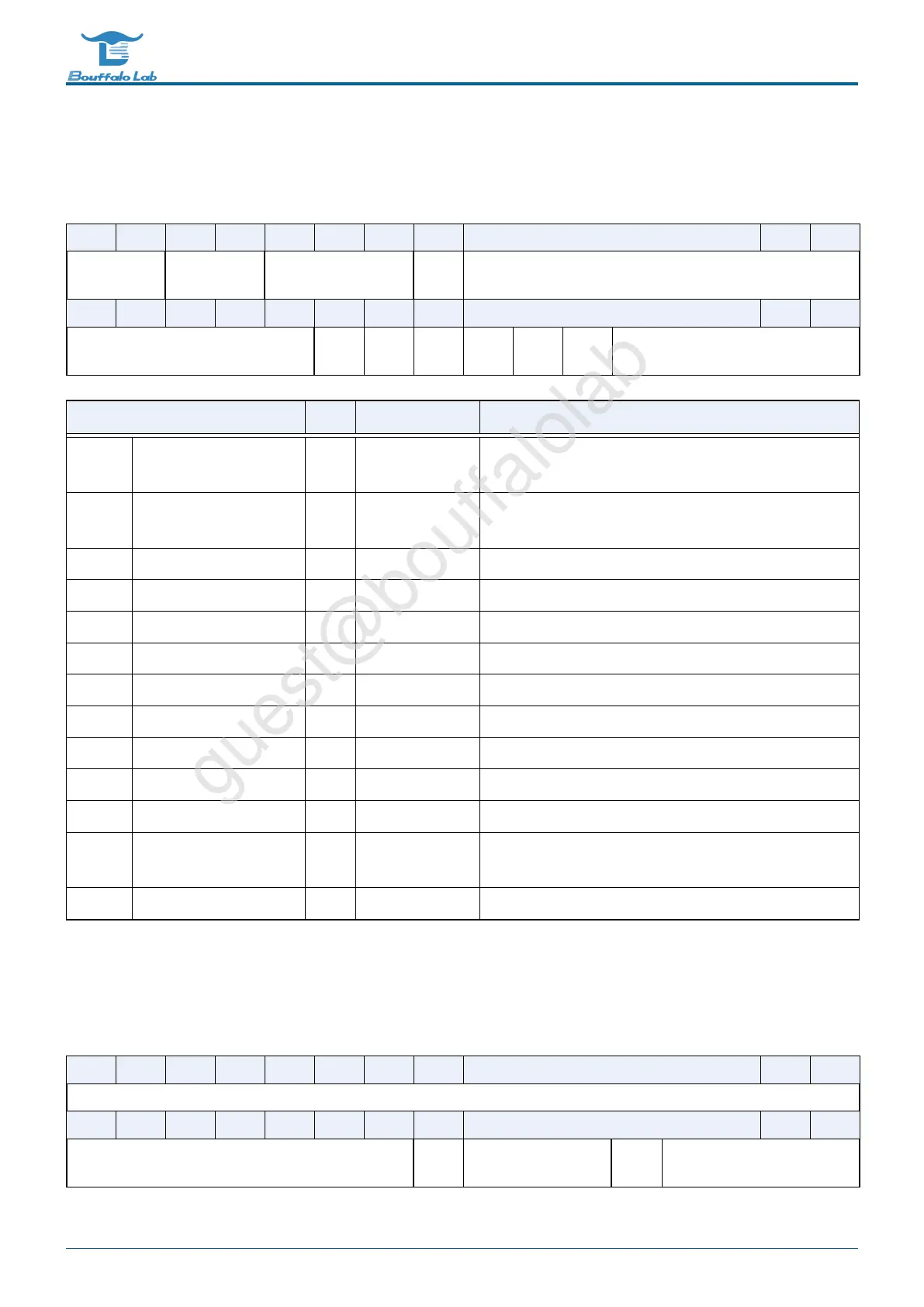

3.3.4 clk_cfg3

Address:0x4000000c

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

CCO1S CCO0S RSVD I2C

EN

I2CDIV

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD ICT

MRX

IRFT

CLK

SPI

EN

ICT

MTX

ICT

PHY

SREF

CLK

SPIDIV

Bits

Name Type Reset Description

31:30 CCO1S R/W 2’b0 clk_out_1 selection (0: no chip clock out, 1: i2s_ref_clk out,

2: audio_pll_clk out, 3: clk_xtal_soc_32M)

29:28 CCO0S R/W 2’b0 clk_out_0 selection (0: no chip clock out, 1: i2s_ref_clk out,

2: audio_pll_clk out, 3: clk_xtal_soc_32M)

27:25 RSVD

24 I2CEN R/W 1 I2C Master Clock Out Enable

23:16 I2CDIV R/W 8’d255 I2C Master Clock Out Divider (Freq_of_BCLK/(N+1))

15:11 RSVD

10 ICTMRX R/W 1’b1 Invert clock to our RMII MAC RX

9 IRFTCLK R/W 1 1: invert rf_test_clk out, 0 : no change

8 SPIEN R/W 1 SPI Clock Enable (Default : Enable)

7 ICTMTX R/W 1’b1 Invert clock to our RMII MAC TX

6 ICTPHY R/W 1’b1 if [5] = 1, set this bit to 1 will invert the clock to RMII PHY

5 SREFCLK R/W 1’b0 0 : select outside 50MHz RMII ref clock, 1: select inside

50MHz RMII ref clock

4:0 SPIDIV R/W 5’d3 SPI Clock Divider (BUS_CLK/(N+1)), default BUS_CLK/4

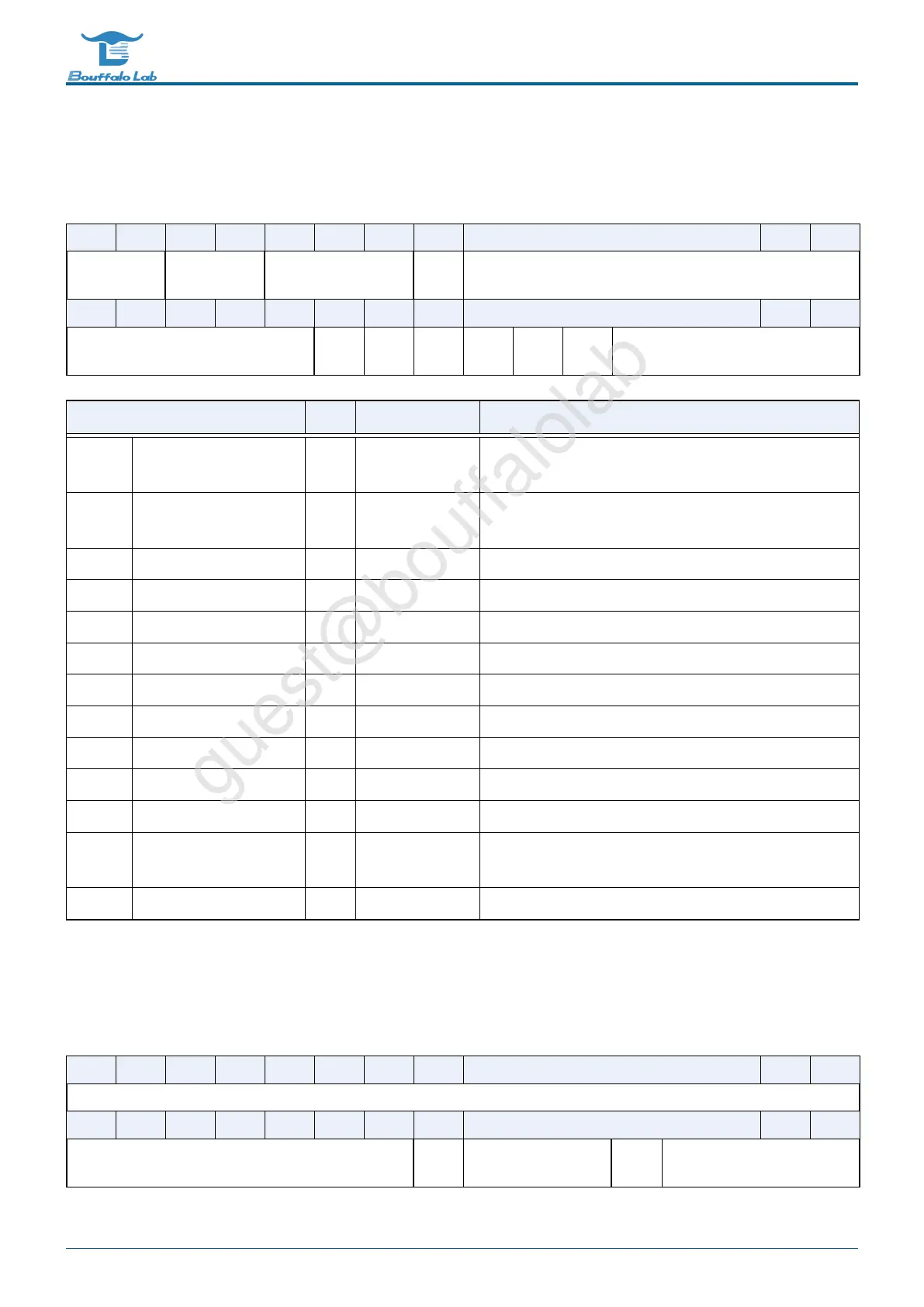

3.3.5 swrst_cfg0

Address:0x40000010

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD SR

S30

RSVD SR

S20

RSVD

BL702/704/706 Reference Manual 43/ 375

@2021 Bouffalo Lab

Loading...

Loading...