BL702/704/706 Reference Manual

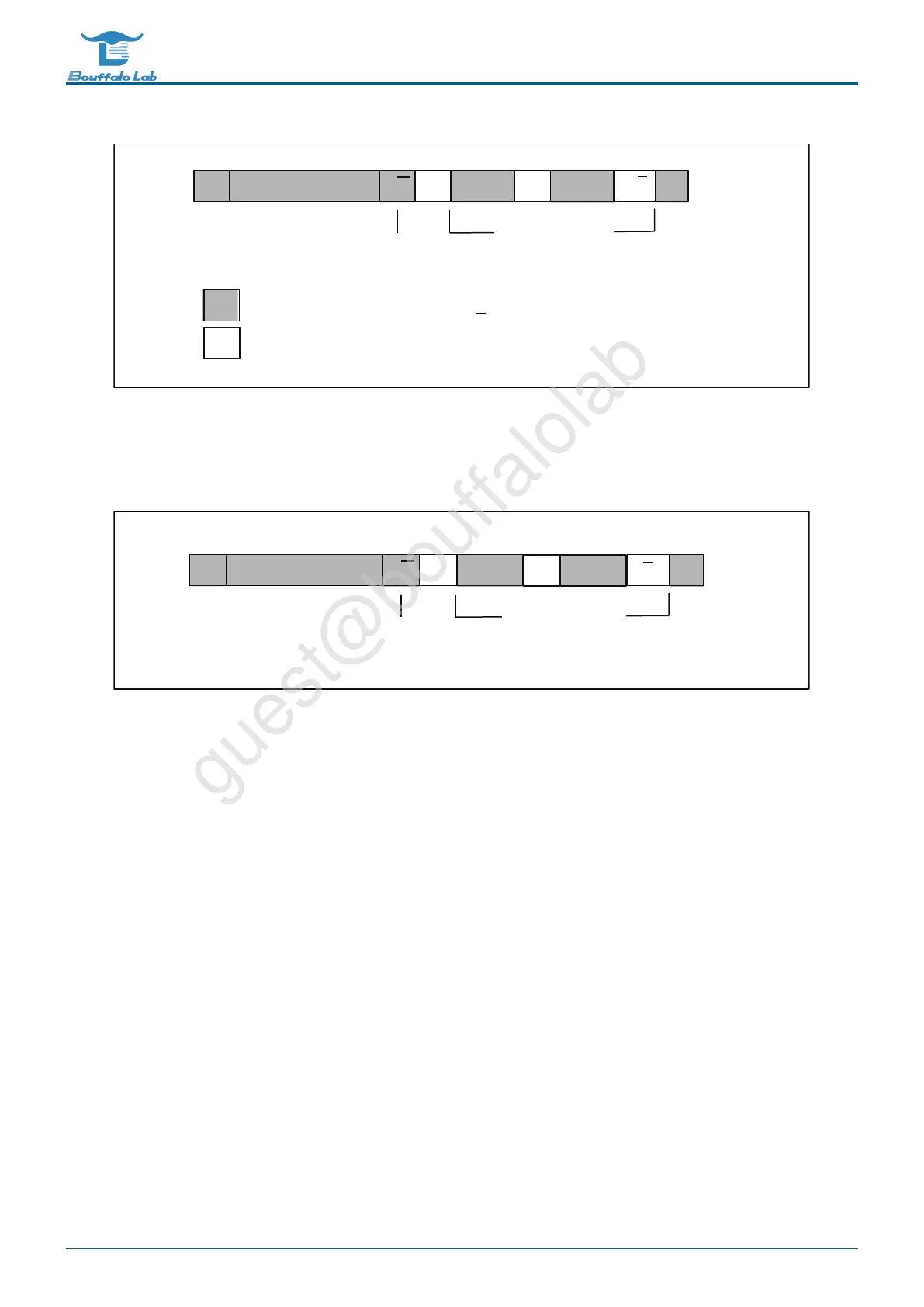

S

SLAVE ADDRESS

R/W

A

DATA

A

DATA

A/A

P

'0'(write)

(n bytes + acknowledge)

data transferred

from master to slave

from slave to master

A = acknowledge(SDA LOW)

A = not acknowledge(SDA HIGH)

S = START condition

P = STOP condition

Fig. 11.3: Master tx and slave rx

Timing of master receive and slave send

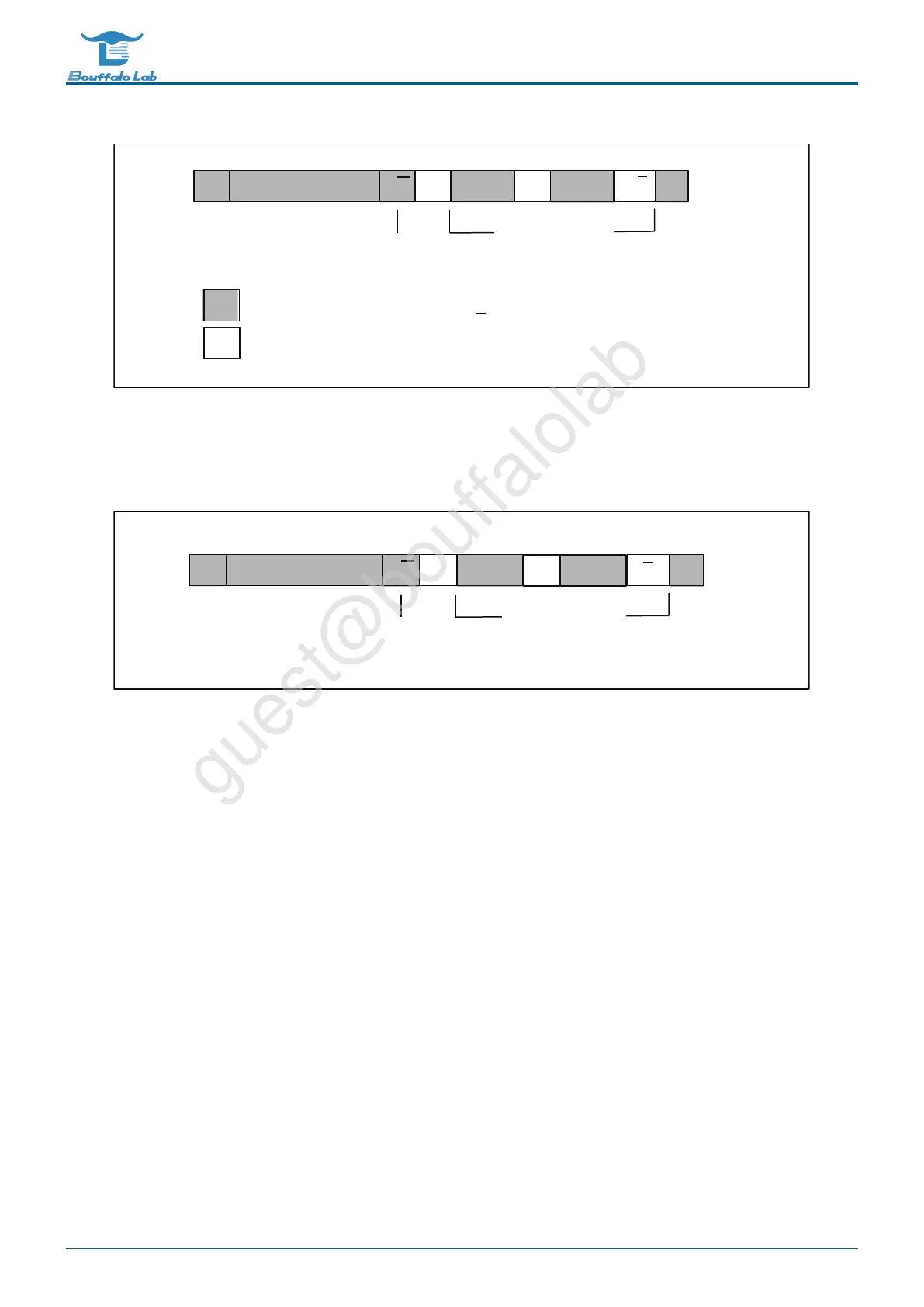

S

SLAVE ADDRESS

R/W

A

DATA

A

DATA

A

P

(read)

(n bytes + acknowledge)

data transferred

1

Fig. 11.4: Master rx and slave tx

11.3.3 Arbitration

When there are multiple masters on the I2C bus, multiple masters may start transmitting at the same time. At this

time, it is necessary to rely on the arbitration mechanism to determine which master has the right to complete the next

data transfer. The remaining masters must give up control of the bus. The transmission cannot be started again until

the bus is free.

During the transmission process, all hosts need to check whether SDA is consistent with the data they want to send

when SCL is high. When the SDA level is different from expected, it means that other hosts are also transmitting at the

same time. Hosts with different SDA levels will lose the arbitration and other hosts will complete the data transmission.

The waveform diagram of two hosts transmitting data and starting the arbitration mechanism at the same time is as

follows:

BL702/704/706 Reference Manual 209/ 375

@2021 Bouffalo Lab

Loading...

Loading...