BL702/704/706 Reference Manual

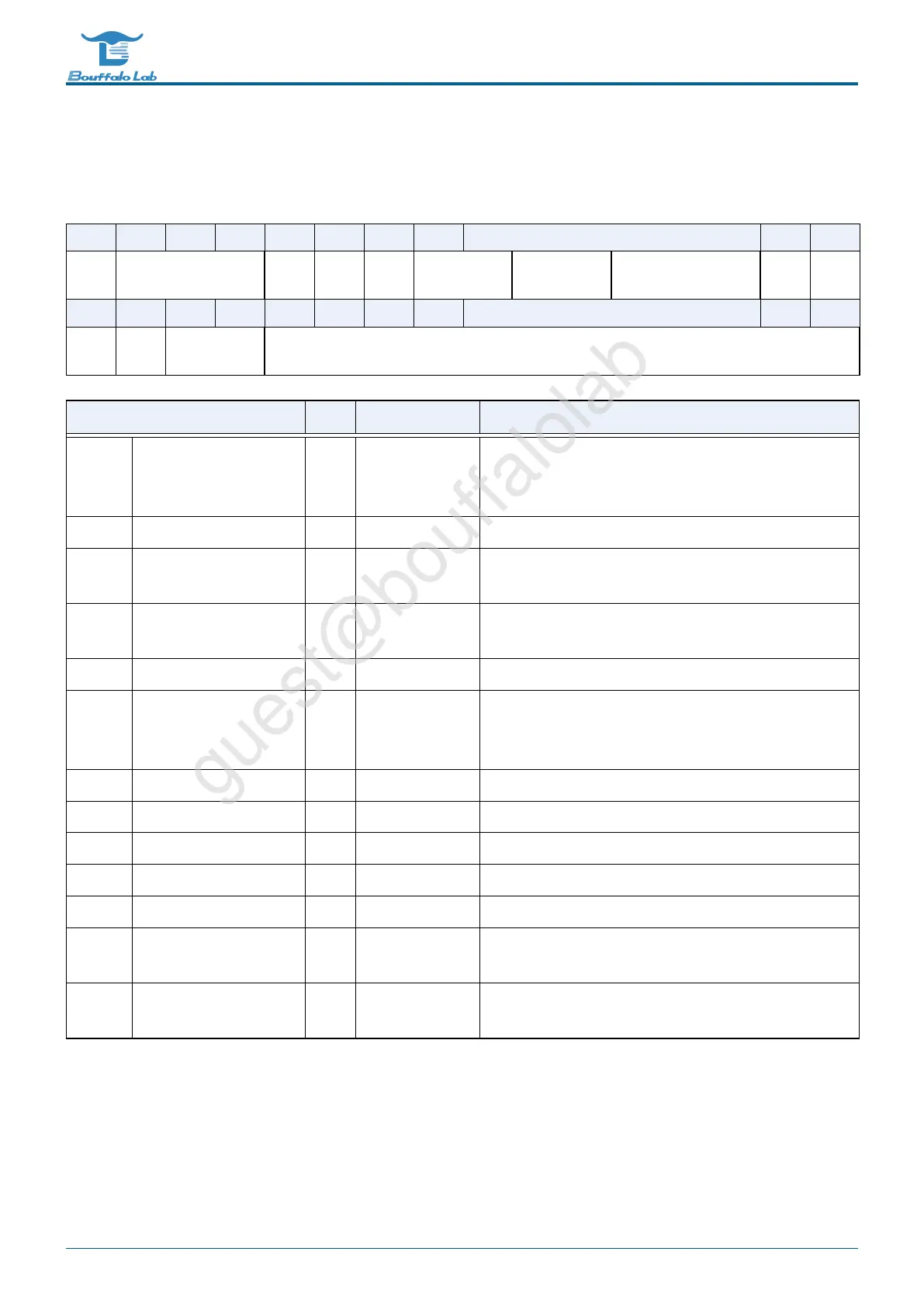

6.5.38 DMA_C4Control

Address:0x4000c50c

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TCI

EN

PROTECT DI SI RSVD FIXCNT DTW STW ADD

MODE

DBS

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DBS MIN

MODE

SBS TS

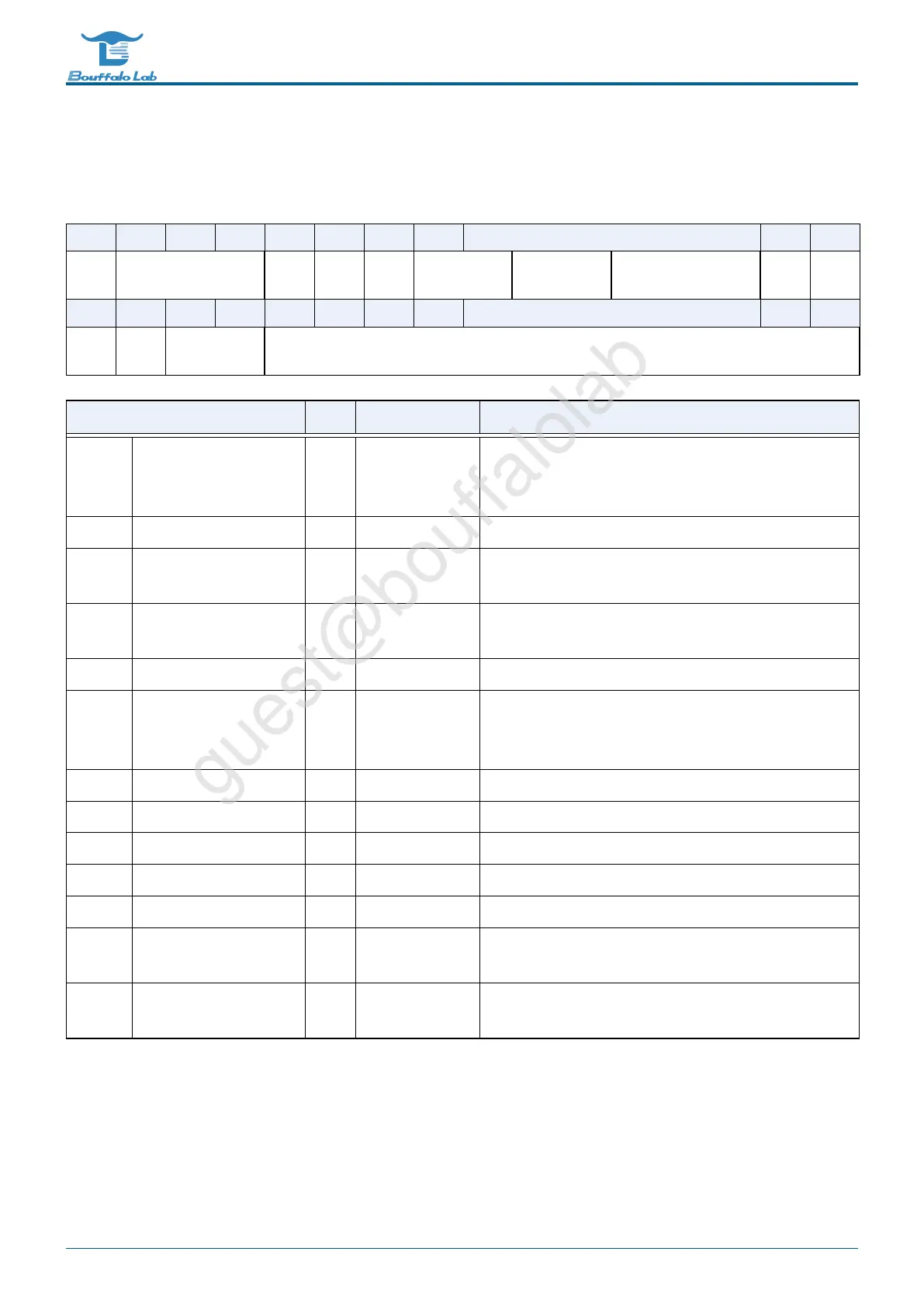

Bits

Name Type Reset Description

31 TCIEN R/W 0 Terminal count interrupt enable bit. It controls whether the

current LLI is expected to trigger the terminal count inter-

rupt.

30:28 PROTECT R/W 0 Protection.

27 DI R/W 1 Destination increment. When set, the Destination address

is incremented after each transfer.

26 SI R/W 1 Source increment. When set, the source address is incre-

mented after each transfer.

25 RSVD

24:23 FIXCNT R/W 2’d0 Only effect when dst_min_mode = 1

Destination transfer cnt = (total src byte cnt - (fix_-

cnt«DWidth))«DWidth

22:21 DTW R/W 3’b010 Destination transfer width: 8/16/32

20:18 STW R/W 3’b010 Source transfer width: 8/16/32

17 ADDMODE R/W 1’b0 Add mode : issue remain destination traffic

16:15 DBS R/W 3’b001 Destination burst size: 1/4/8/16

14 MINMODE R/W 1’b0 Minus mode : Not issue all destination traffic

13:12 SBS R/W 3’b001 Source burst size: 1/4/8/16. Note CH FIFO Size is 16Bytes

and SBSize*Swidth should <= 16B

11:0 TS R/W 0 Transfer size: 0 4095. Number of data transfers left to com-

plete when the SMDMA is the flow controller.

BL702/704/706 Reference Manual 147/ 375

@2021 Bouffalo Lab

Loading...

Loading...