BL702/704/706 Reference Manual

Bits

Name Type Reset Description

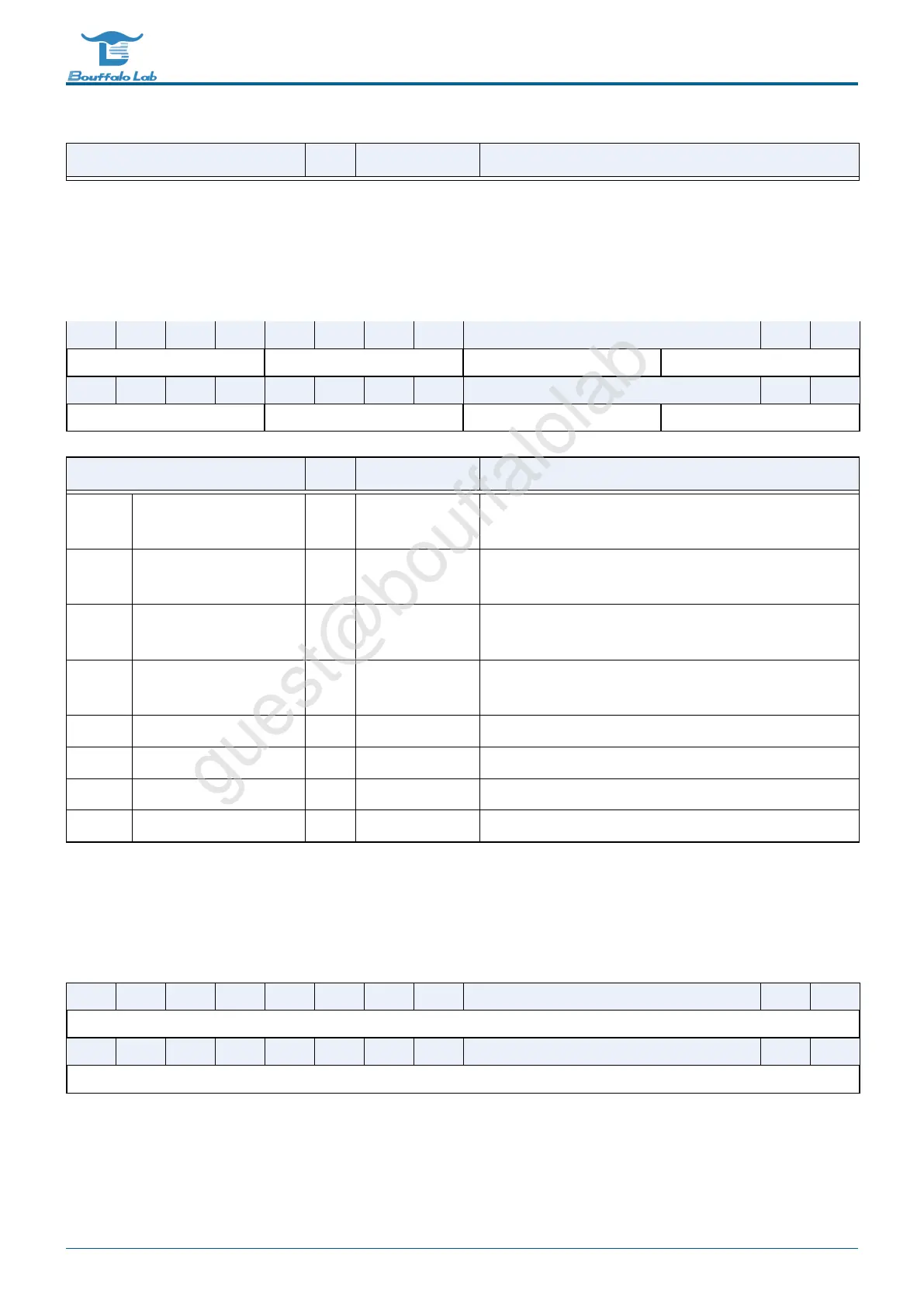

8.4.6 irtx_pw

Address:0x4000a614

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TXTPH1W TXTPH0W TXHPH1W TXHPH0W

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TXL1PH1W TXL1PH0W TXL0PH1W TXL0PH0WS

Bits

Name Type Reset Description

31:28 TXTPH1W R/W 4’d0 Pulse width of tail pulse phase 1 (Don’t care if SWM is en-

abled)

27:24 TXTPH0W R/W 4’d0 Pulse width of tail pulse phase 0 (Don’t care if SWM is en-

abled)

23:20 TXHPH1W R/W 4’d7 Pulse width of head pulse phase 1 (Don’t care if SWM is

enabled)

19:16 TXHPH0W R/W 4’d15 Pulse width of head pulse phase 0 (Don’t care if SWM is

enabled)

15:12 TXL1PH1W R/W 4’d2 Pulse width of logic1 phase 1 (Don’t care if SWM is enabled)

11:8 TXL1PH0W R/W 4’d0 Pulse width of logic1 phase 0 (Don’t care if SWM is enabled)

7:4 TXL0PH1W R/W 4’d0 Pulse width of logic0 phase 1 (Don’t care if SWM is enabled)

3:0 TXL0PH0WS R/W 4’d0 Pulse width of logic0 phase 0 (Don’t care if SWM is enabled)

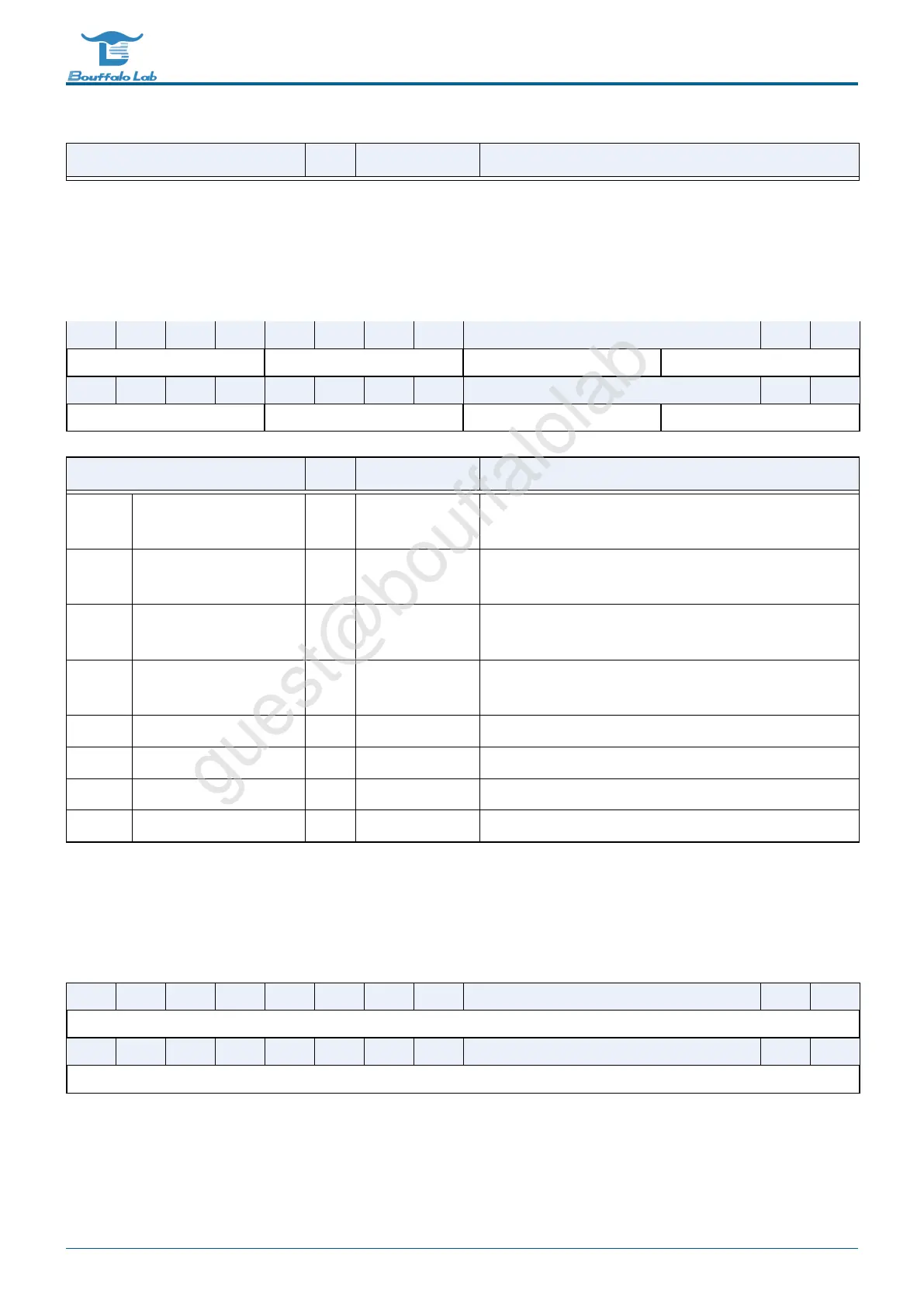

8.4.7 irtx_swm_pw_0

Address:0x4000a640

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TXSWPW0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TXSWPW0

BL702/704/706 Reference Manual 170/ 375

@2021 Bouffalo Lab

Loading...

Loading...