BL702/704/706 Reference Manual

Name

Description

TCVSYN2 Timer2 synchronous value of counter register

TCVSYN3 Timer3 synchronous value of counter register

TCDR WDT/Timer clock division register

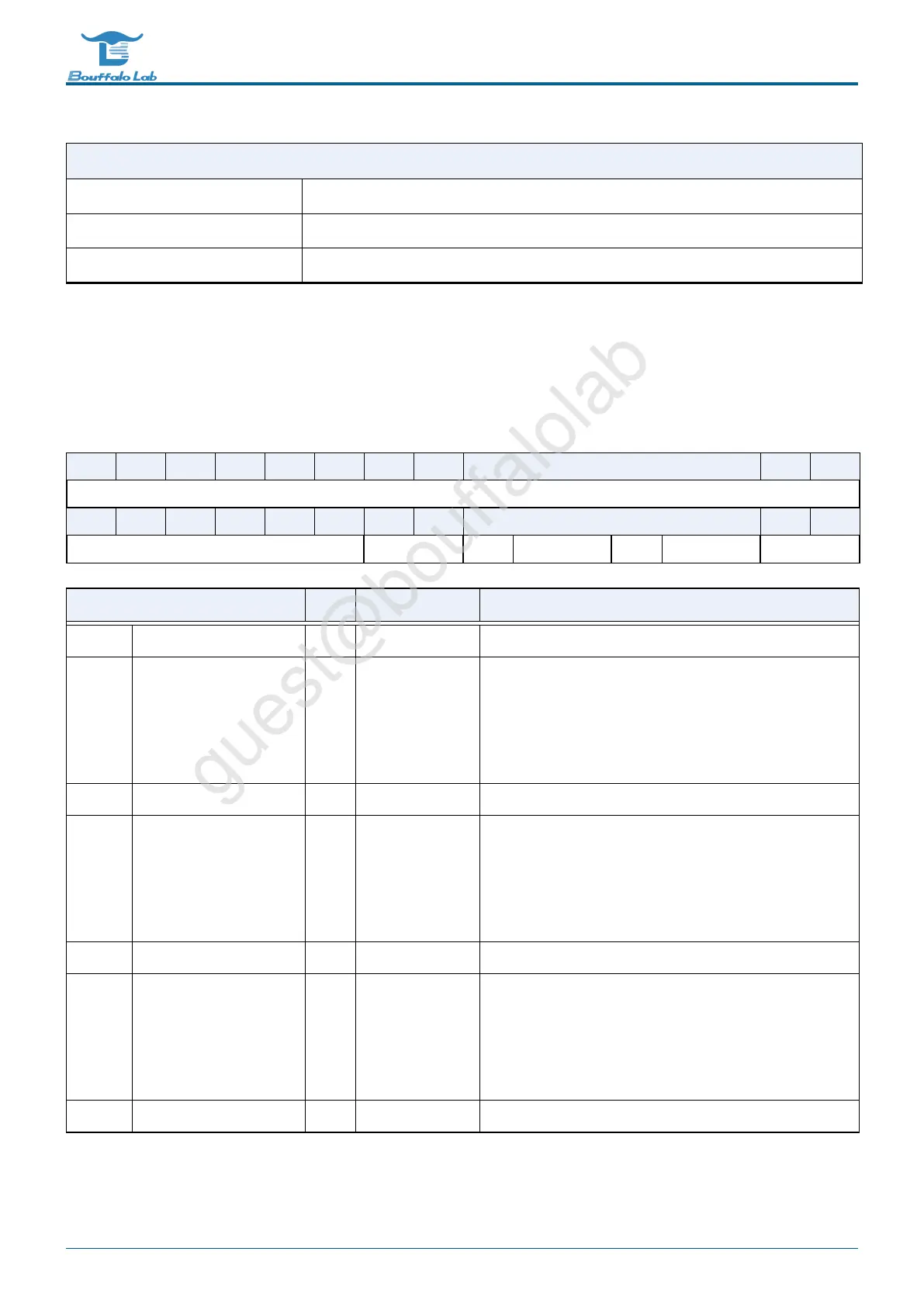

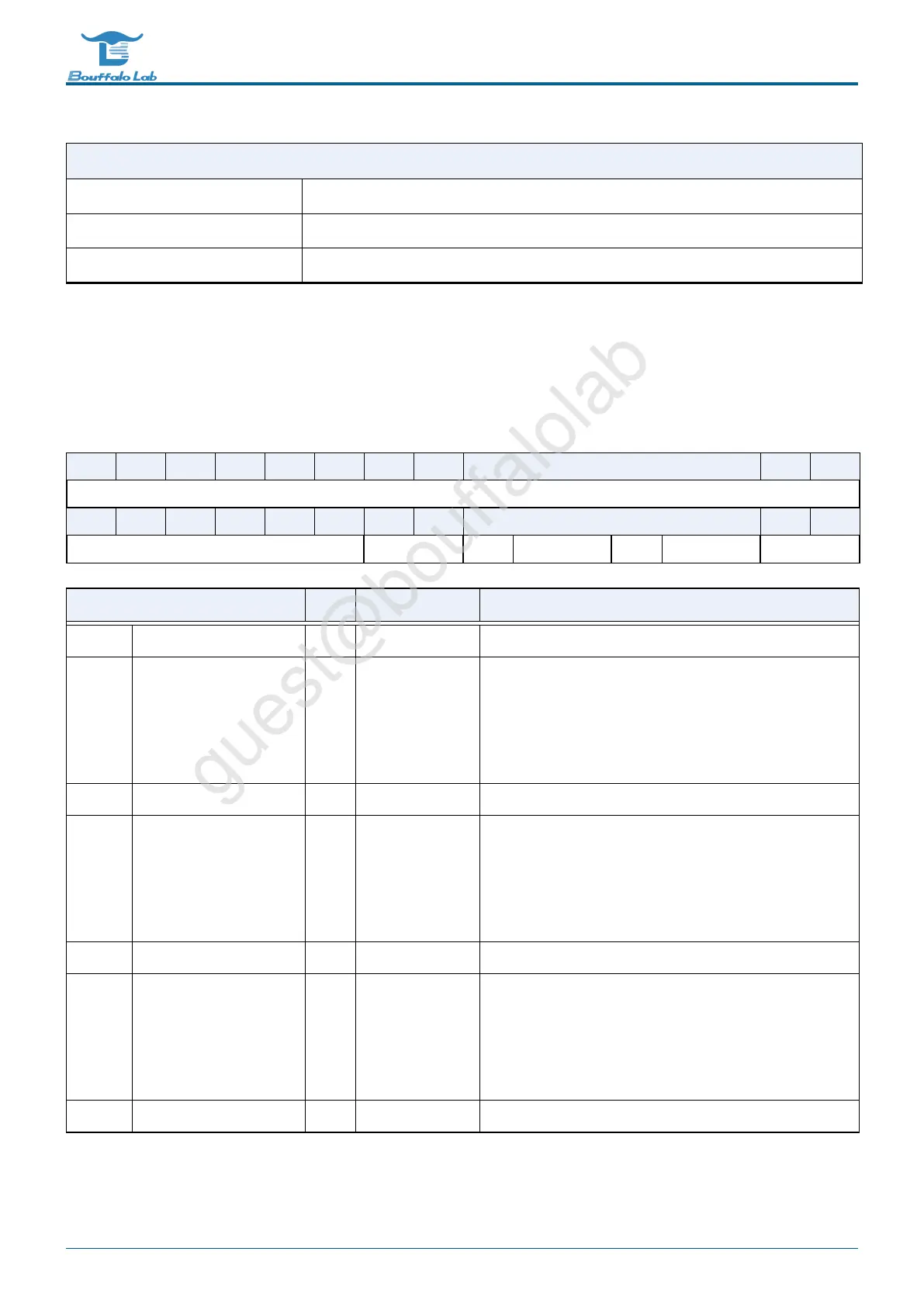

13.4.1 TCCR

Address:0x4000a500

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD CSWDT RSVD CS2 RSVD CS1 RSVD

Bits

Name Type Reset Description

31:10 RSVD

9:8 CSWDT R/W 2’d0 Clock Source for Timer #1/#2/#3/WDT

2’d0 - fclk

2’d1 - f32k_clk

2’d2 - 1 kHz

2’d3 - PLL 32MHz

7 RSVD

6:5 CS2 R/W 2’d0 Clock Source for Timer #1/#2/#3/WDT

2’d0 - fclk

2’d1 - f32k_clk

2’d2 - 1 kHz

2’d3 - PLL 32MHz

4 RSVD

3:2 CS1 R/W 2’d0 Clock Source for Timer #1/#2/#3/WDT

2’d0 - fclk

2’d1 - f32k_clk

2’d2 - 1 kHz

2’d3 - PLL 32MHz

1:0 RSVD

BL702/704/706 Reference Manual 246/ 375

@2021 Bouffalo Lab

Loading...

Loading...