BL702/704/706 Reference Manual

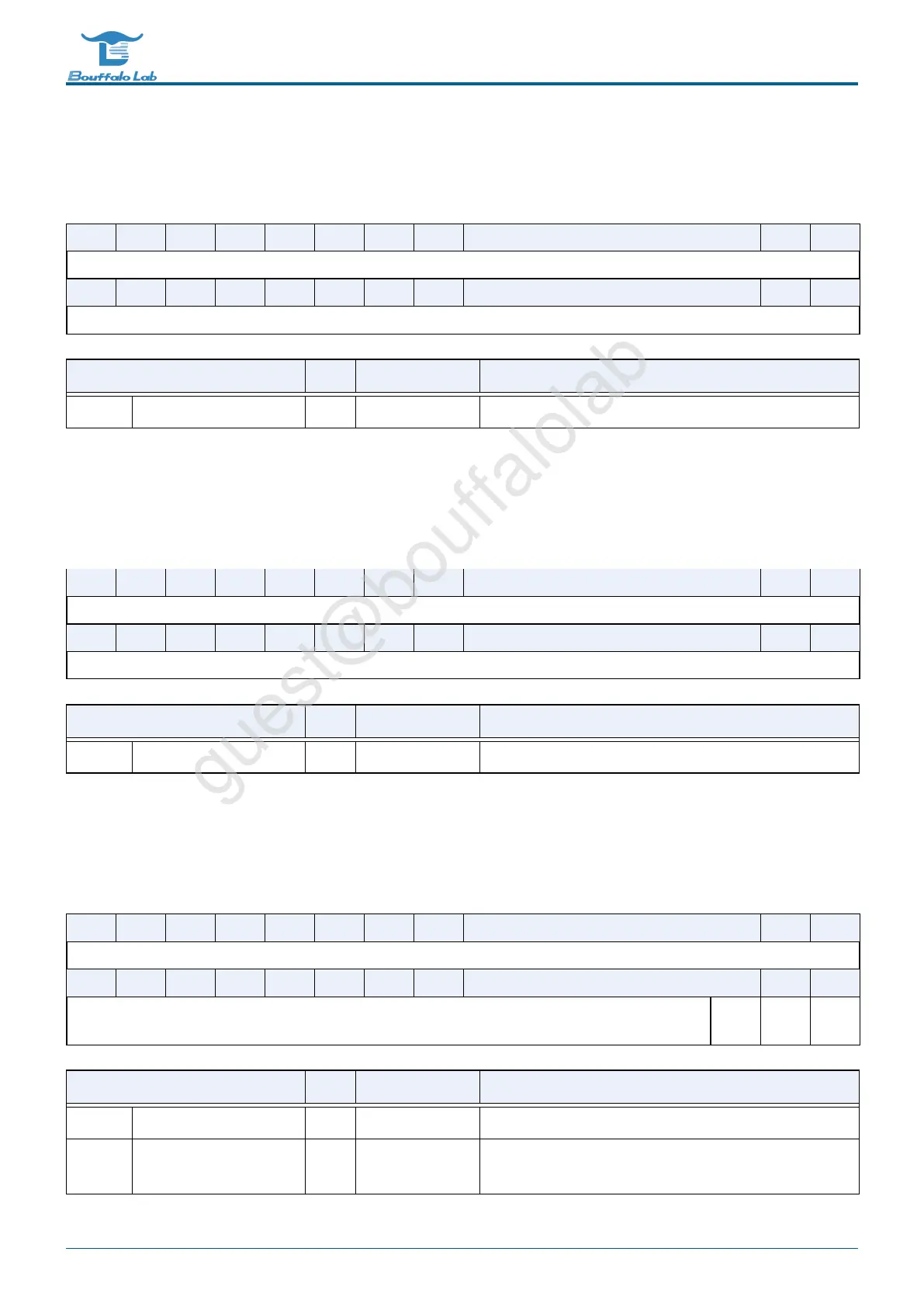

13.4.8 TCR2

Address:0x4000a52c

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TCR2COUT

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TCR2COUT

Bits

Name Type Reset Description

31:0 TCR2COUT R 32’h0 Timer2 counter register

13.4.9 TCR3

Address:0x4000a530

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TCR3COUT

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TCR3COUT

Bits

Name Type Reset Description

31:0 TCR3COUT R 32’h0 Timer3 counter register

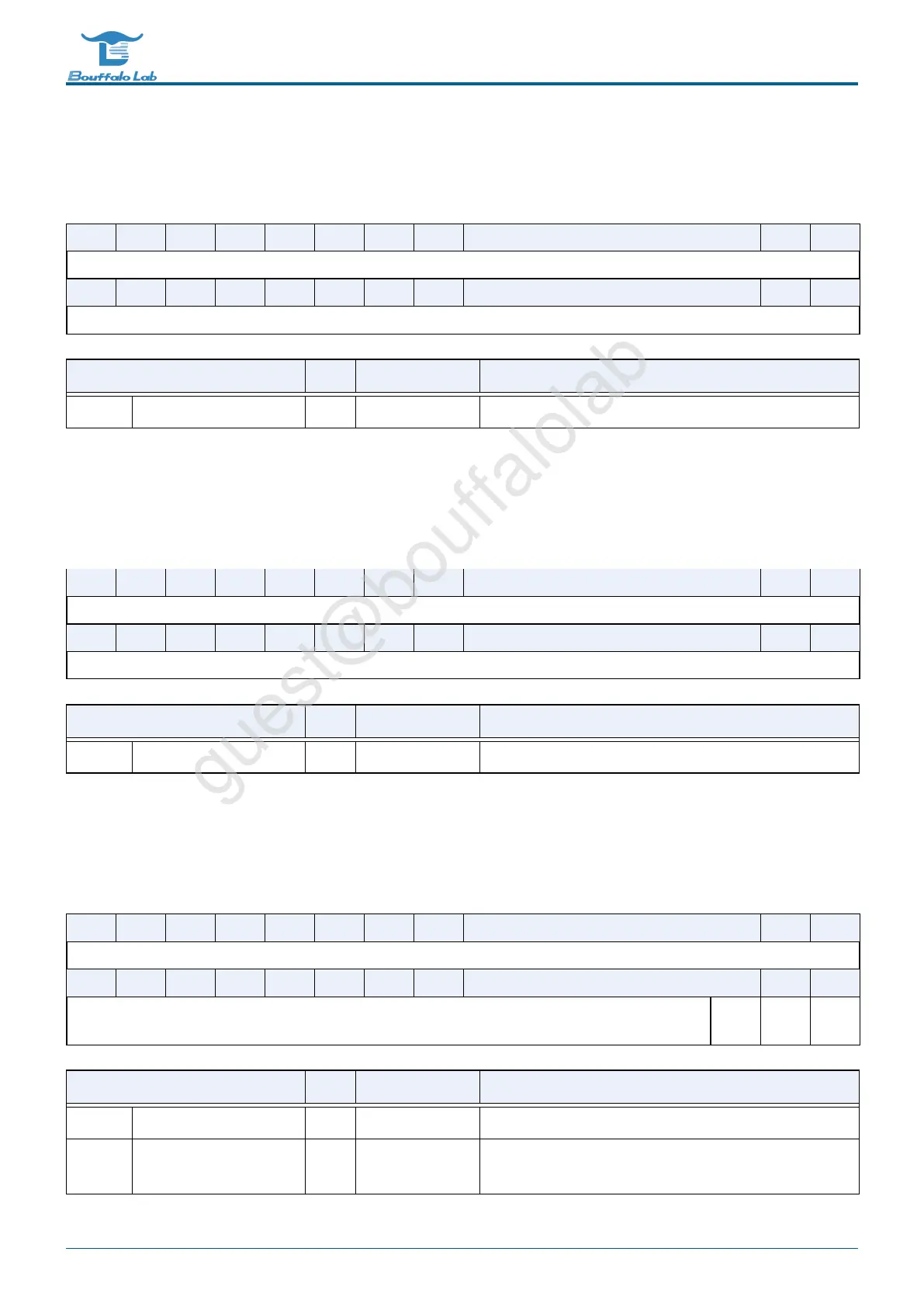

13.4.10 TMSR2

Address:0x4000a538

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD T2M

R2S

T2M

R1S

T2M

R0S

Bits

Name Type Reset Description

31:3 RSVD

2 T2MR2S R 1’b0 Timer2 match register 2 status/Clear interrupt would also

clear this bit

BL702/704/706 Reference Manual 249/ 375

@2021 Bouffalo Lab

Loading...

Loading...