BL702/704/706 Reference Manual

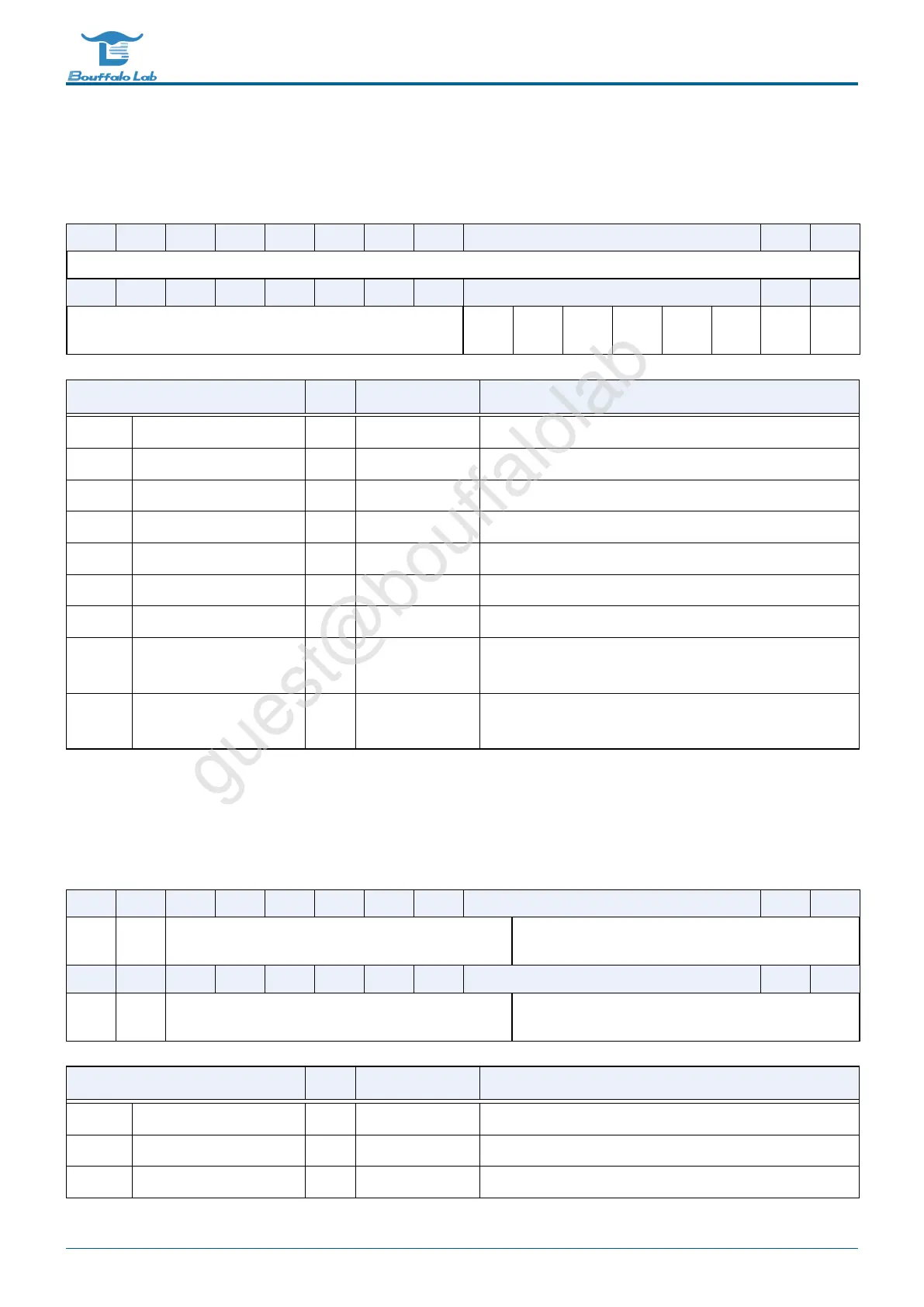

18.4.45 ep7_fifo_config

Address:0x4000d970

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD E7

RFU

E7

RFO

E7

TFU

E7

TFO

E7

RFC

E7

TFC

E7

DREN

E7

DTEN

Bits

Name Type Reset Description

31:8 RSVD

7 E7RFU R 1’b0 Underflow flag of RX FIFO, can be cleared by rx_fifo_clr

6 E7RFO R 1’b0 Overflow flag of RX FIFO, can be cleared by rx_fifo_clr

5 E7TFU R 1’b0 Underflow flag of TX FIFO, can be cleared by tx_fifo_clr

4 E7TFO R 1’b0 Overflow flag of TX FIFO, can be cleared by tx_fifo_clr

3 E7RFC W1C 1’b0 Clear signal of RX FIFO

2 E7TFC W1C 1’b0 Clear signal of TX FIFO

1 E7DREN R/W 1’b0 Enable signal of dma_rx_req/ack interface

Set 1 when use DMA for rx FIFO data transfer

0 E7DTEN R/W 1’b0 Enable signal of dma_tx_req/ack interface

Set 1 when use DMA for tx FIFO data transfer

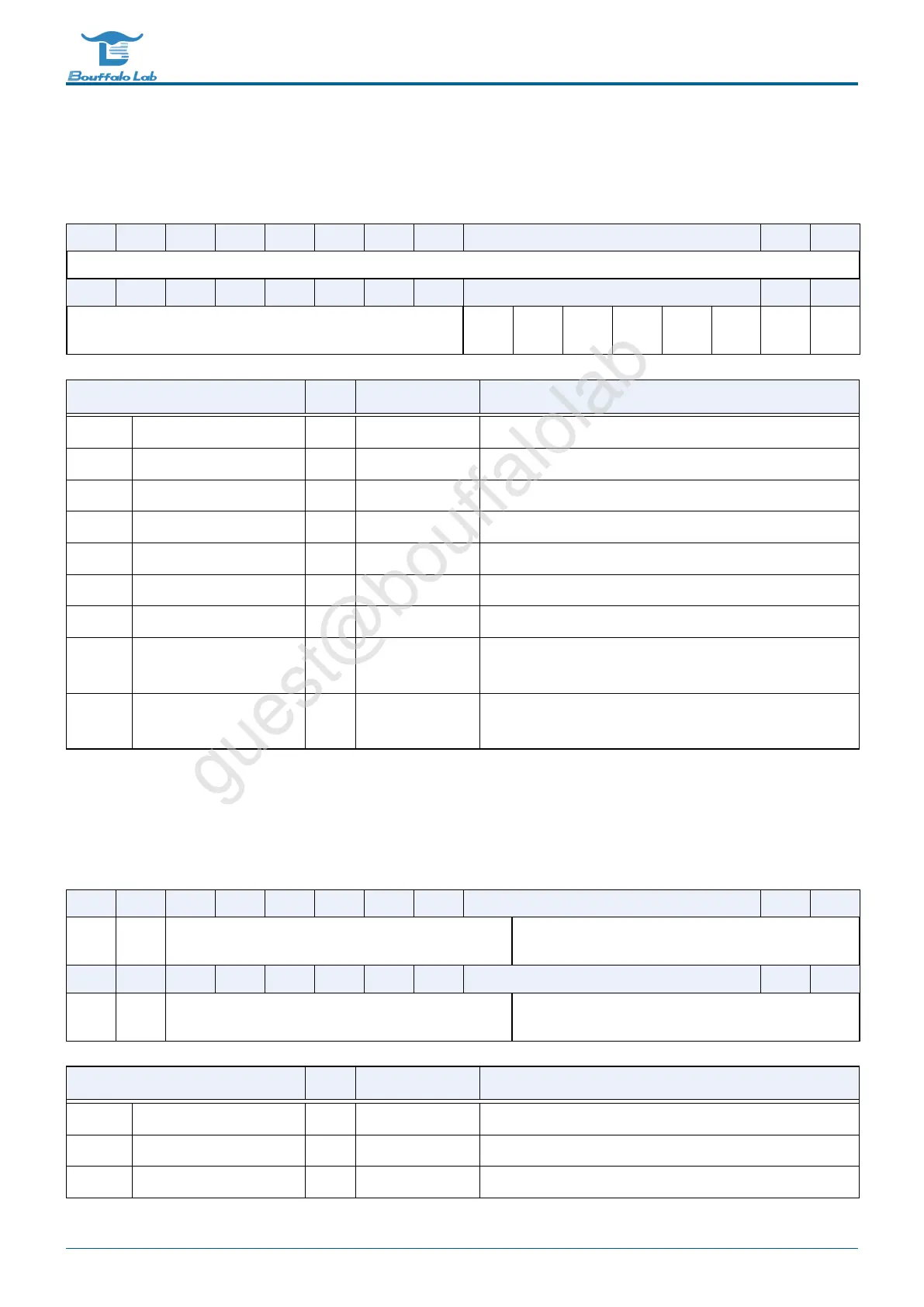

18.4.46 ep7_fifo_status

Address:0x4000d974

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

E7

RFF

E7

RFE

RSVD E7RFC

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

E7

TFF

E7

TFE

RSVD E7TFC

Bits

Name Type Reset Description

31 E7RFF R 1’b0 RX FIFO full flag

30 E7RFE R 1’b1 RX FIFO empty flag

29:23 RSVD

BL702/704/706 Reference Manual 347/ 375

@2021 Bouffalo Lab

Loading...

Loading...