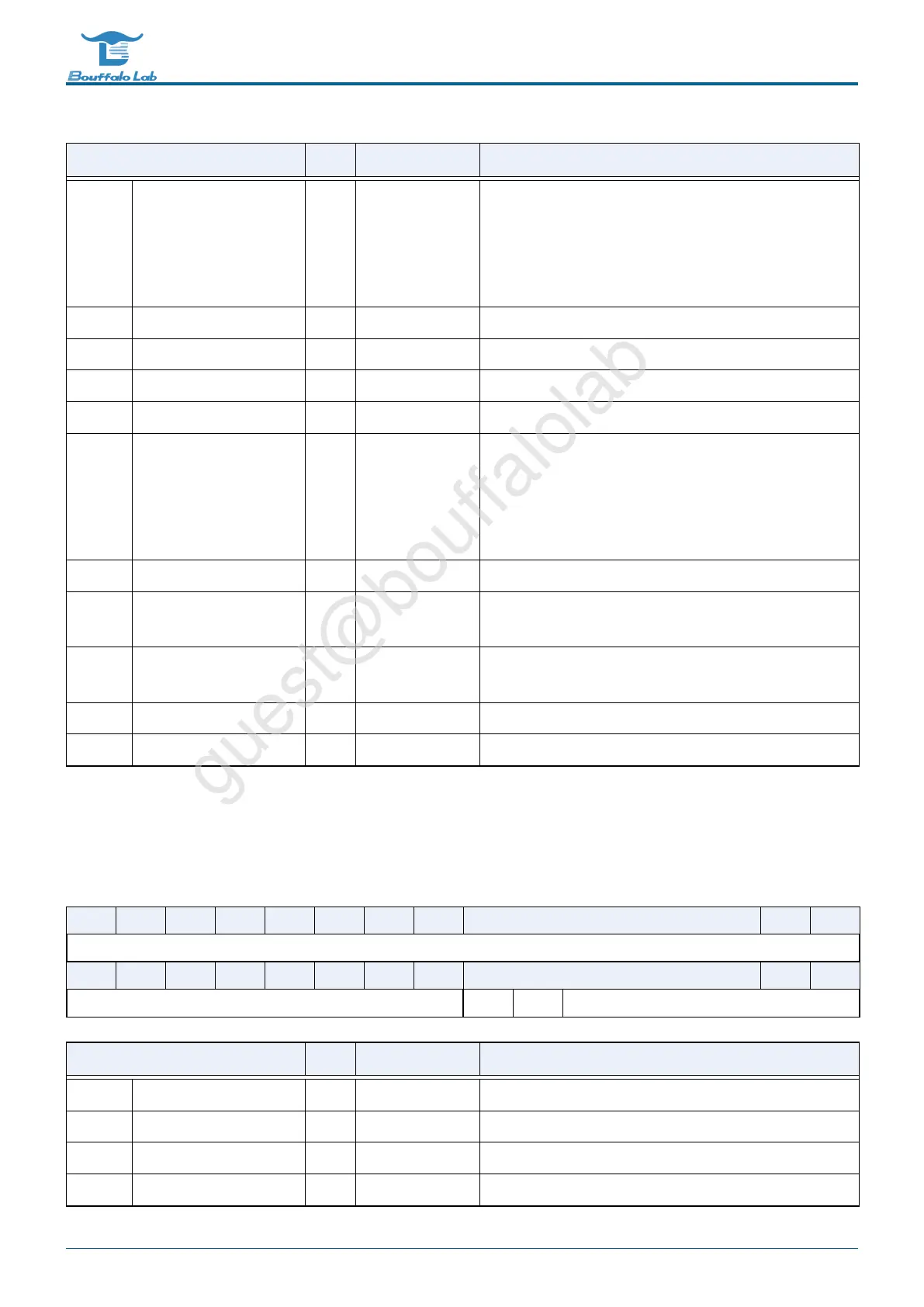

BL702/704/706 Reference Manual

Bits

Name Type Reset Description

27:24 RTIDOVEC R/W 4’ha ldo output voltage external control:

0:0.60V, 1:0.65V, 2:0.70V, 3:0.75V, 4:0.80V, 5:0.85V,

6:0.9V, 7:0.95V

8:1.0V, 9:1.05V, 10:1.1V, 11:1.15V, 12:1.2V, 13:1.25V,

14:1.3V, 15:1.35V

23:20 RSVD

19:16 V11SOVSEL R/W 4’hA vdd11soc output voltage selection

15:14 RSVD

13 CRSE R/W 1’b0 clear reset event

12:8 HBNRSEV R 4’b0 [4] : bor_out_ event

[3] : pwr_rst_n event

[2] : sw_rst event

[1] : ext_rst_n event

[0] : por_out event

7:6 R/W 2’h1 ldo11_rt drive strength select

5 PURC32 R/W 1 0: Turn off rc32k during rtc power domain off, 1: Don’t turn

off rc32k

4:3 F32SEL R/W 0 32KHz clock source selection (0: RC32K 1: XTAL 32K 3:

DIG 32K)

2 UARTCLK R/W 0 uart clock selection from HBN (0:fclk 1:96MHz)

1:0 ROOTCLK R/W 0 root clock source selection (0: RC32M 1: XTAL 2/3: PLL)

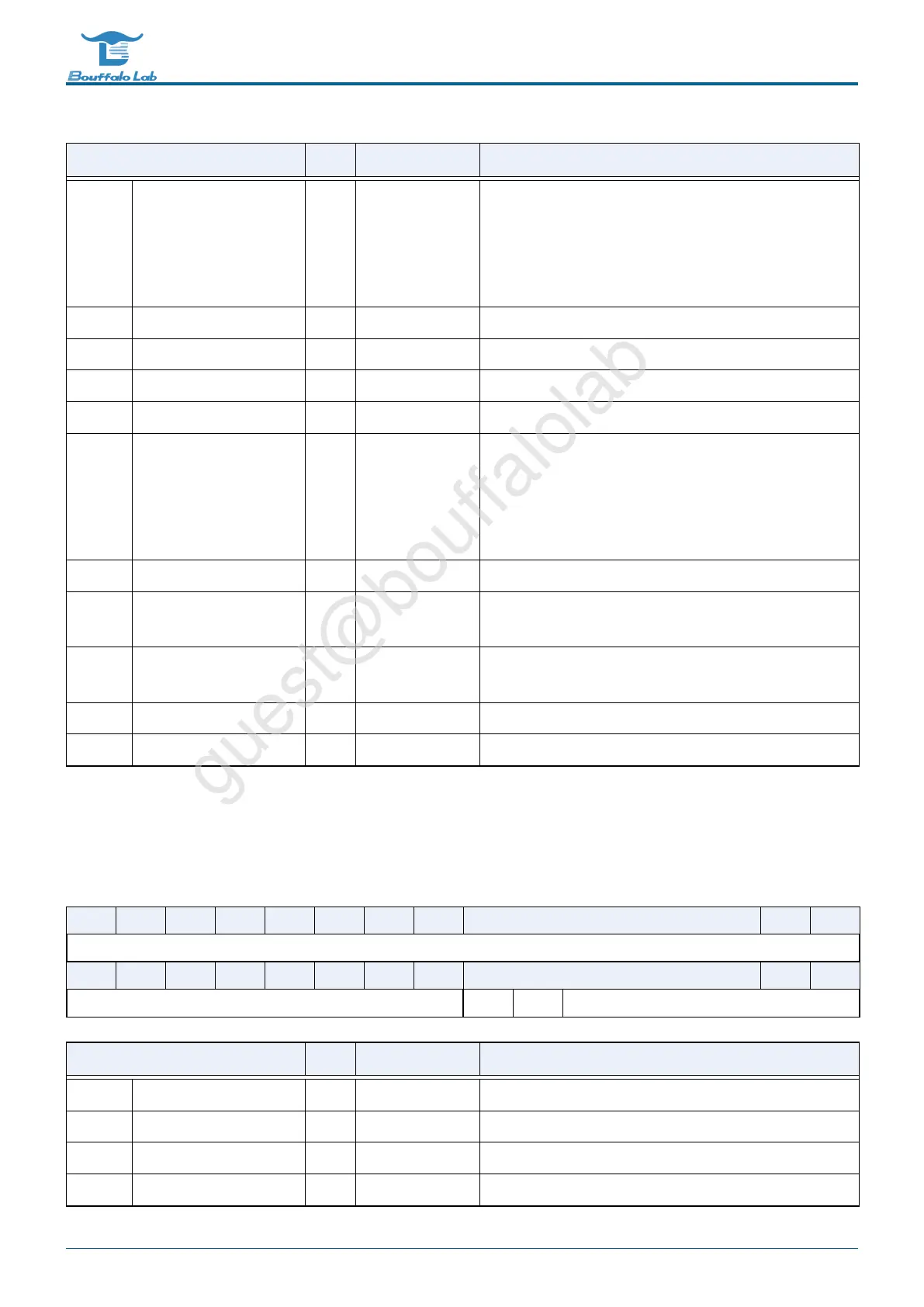

19.4.14 HBN_SRAM

Address:0x4000f034

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD SLP RET RSVD

Bits

Name Type Reset Description

31:8 RSVD

7 SLP R/W 0 make HBN RAM Sleep

6 RET R/W 0 make HBN RAM Retention

5:0 RSVD

BL702/704/706 Reference Manual 362/ 375

@2021 Bouffalo Lab

Loading...

Loading...