Vectored Interrupt Controller (VIC) 100 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

Interrupt Enable Register (VICIntEnable - 0xFFFFF010, Read/Write)

This register controls which of the 32 interrupt requests and software interrupts contribute to FIQ or IRQ.

Interrupt Enable Clear Register (VICIntEnClear - 0xFFFFF014, Write Only)

This register allows software to clear one or more bits in the Interrupt Enable register, without having to first read it.

Interrupt Select Register (VICIntSelect - 0xFFFFF00C, Read/Write)

This register classifies each of the 32 interrupt requests as contributing to FIQ or IRQ.

IRQ Status Register (VICIRQStatus - 0xFFFFF000, Read Only)

This register reads out the state of those interrupt requests that are enabled and classified as IRQ. It does not differentiate

between vectored and non-vectored IRQs.

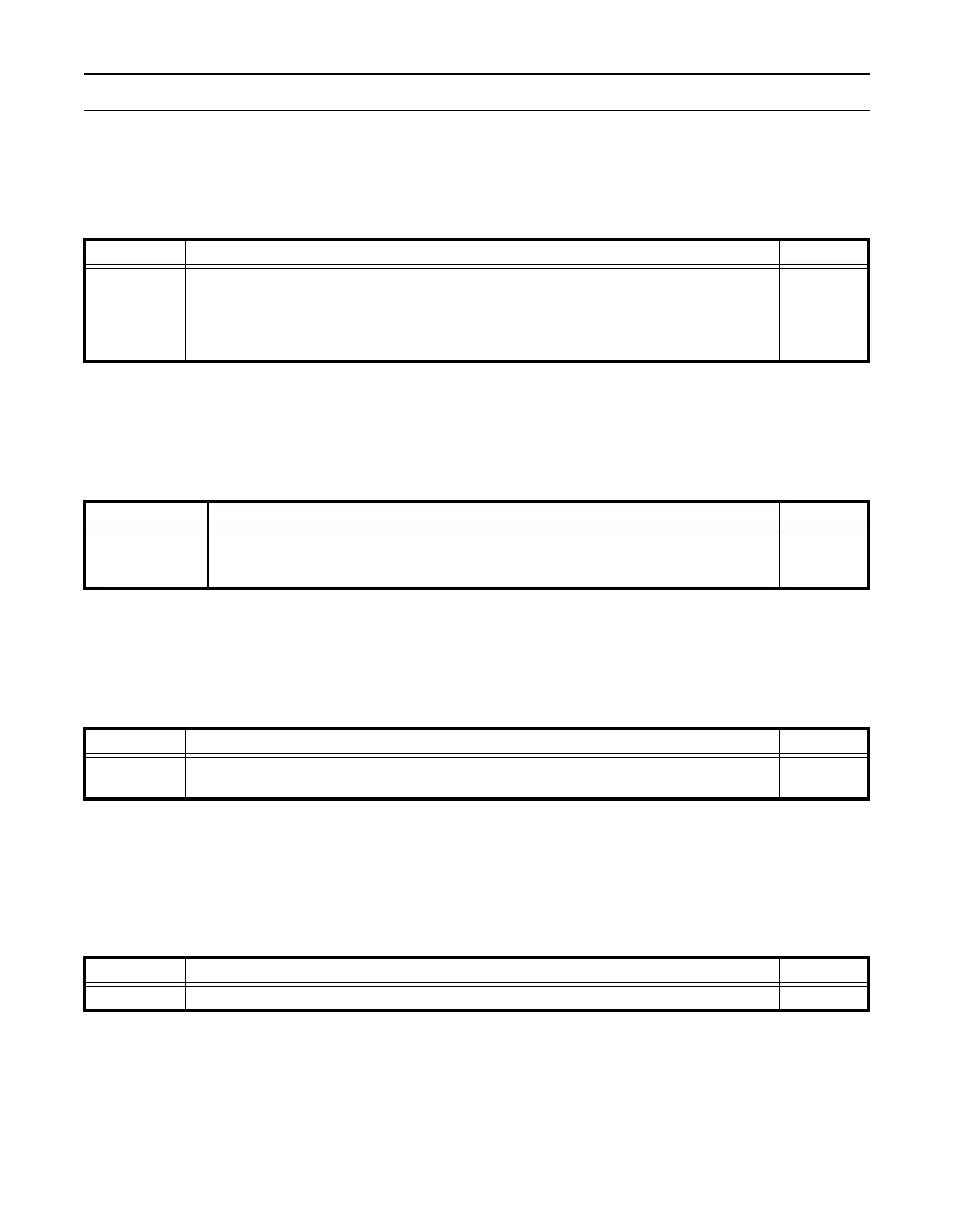

Table 44: Interrupt Enable Register (VICINtEnable - 0xFFFFF010, Read/Write)

VICIntEnable Function Reset Value

31:0

When this register is read, 1s indicate interrupt requests or software interrupts that are enabled

to contribute to FIQ or IRQ.

When this register is written, ones enable interrupt requests or software interrupts to contribute

to FIQ or IRQ, zeroes have no effect. See the VICIntEnClear register (Table 45 below), for how

to disable interrupts.

0

Table 45: Software Interrupt Clear Register (VICIntEnClear - 0xFFFFF014, Write Only)

VICIntEnClear Function Reset Value

31:0

1: writing a 1 clears the corresponding bit in the Interrupt Enable register, thus disabling

interrupts for this request.

0: writing a 0 leaves the corresponding bit in VICIntEnable unchanged.

0

Table 46: Interrupt Select Register (VICIntSelect - 0xFFFFF00C, Read/Write)

VICIntSelect Function Reset Value

31:0

1: the interrupt request with this bit number is assigned to the FIQ category.

0: the interrupt request with this bit number is assigned to the IRQ category.

0

Table 47: IRQ Status Register (VICIRQStatus - 0xFFFFF000, Read-Only)

VICIRQStatus Function Reset Value

31:0 1: the interrupt request with this bit number is enabled, classified as IRQ, and asserted. 0

Loading...

Loading...