Memory Accelerator Module (MAM) 94 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

MAM Control Register (MAMCR - 0xE01FC000)

Two configuration bits select the three MAM operating modes, as shown in Table 38. Following Reset, MAM functions are

disabled. Changing the MAM operating mode causes the MAM to invalidate all of the holding latches, resulting in new reads of

Flash information as required.

MAM Timing Register (MAMTIM - 0xE01FC004)

The MAM Timing register determines how many cclk cycles are used to access the Flash memory. This allows tuning MAM timing

to match the processor operating frequency. Flash access times from 1 clock to 7 clocks are possible. Single clock Flash

accesses would essentially remove the MAM from timing calculations. In this case the MAM mode may be selected to optimize

power usage.

MAM USAGE NOTES

When changing MAM timing, the MAM must first be turned off by writing a zero to MAMCR. A new value may then be written to

MAMTIM. Finally, the MAM may be turned on again by writing a value (1 or 2) corresponding to the desired operating mode to

MAMCR.

For system clock slower than 20 MHz, MAMTIM can be 001. For system clock between 20 MHz and 40 MHz, Flash access time

is suggested to be 2 CCLKs, while in systems with system clock faster than 40 MHz, 3 CCLKs are proposed.

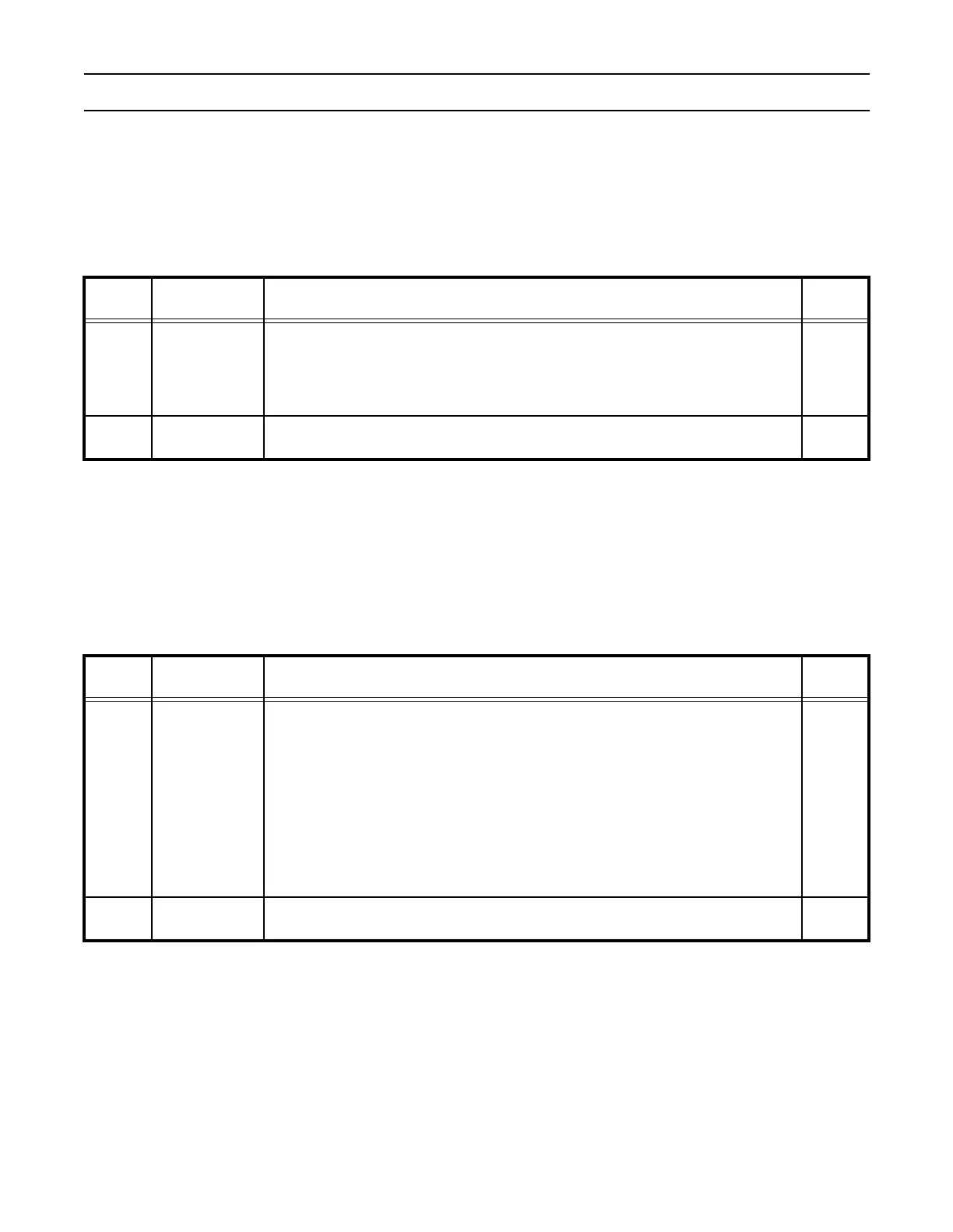

Table 38: MAM Control Register (MAMCR - 0xE01FC000)

MAMCR Function Description

Reset

Value

1:0

MAM mode

control

These bits determine the operating mode of the MAM as follows:

0 0 - MAM functions disabled.

0 1 - MAM functions partially enabled.

1 0 - MAM functions fully enabled.

1 1 - reserved

0

7:2 Reserved

Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

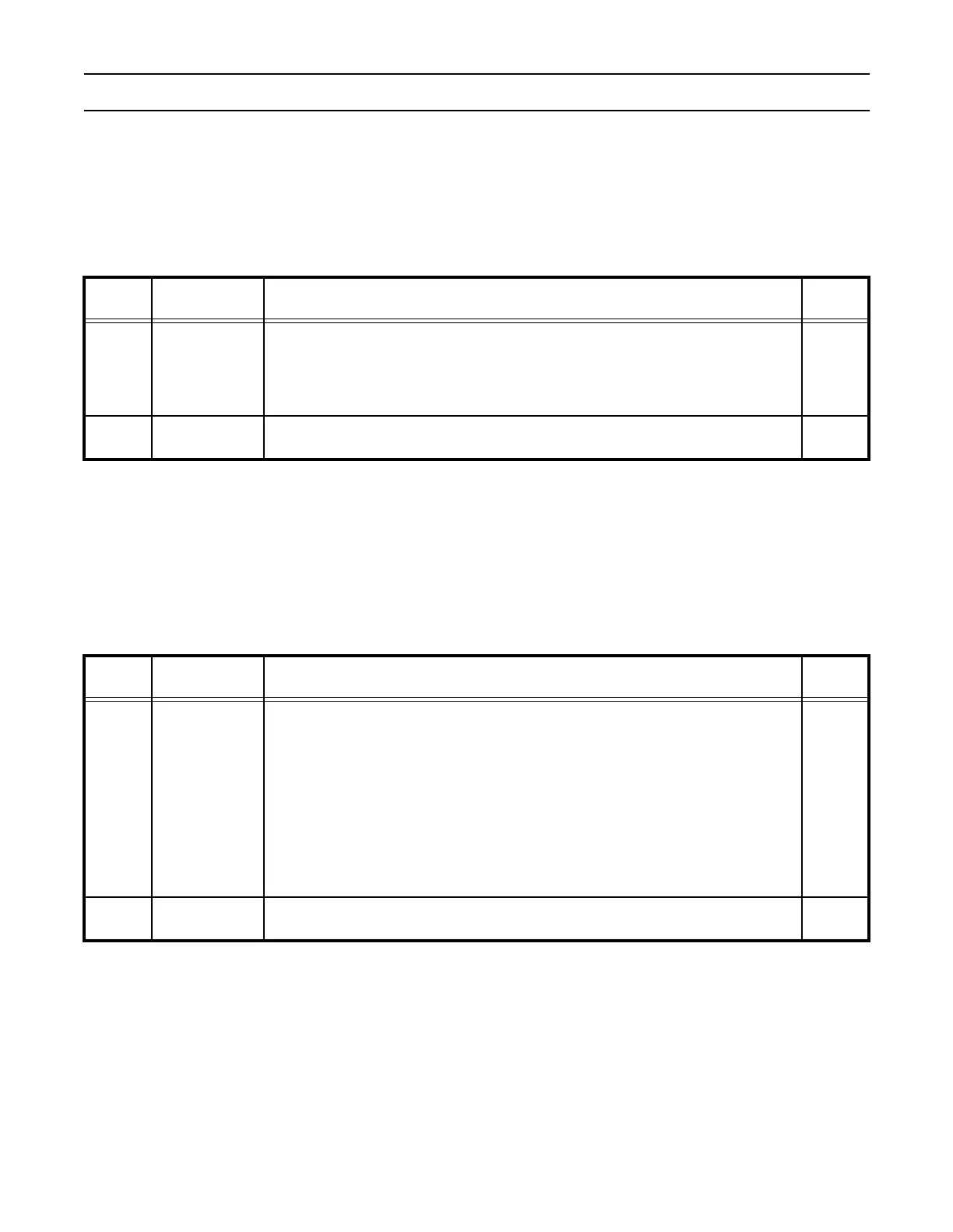

Table 39: MAM Timing Register (MAMTIM - 0xE01FC004)

MAMTIM Function Description

Reset

Value

2:0

MAM Fetch

Cycle timing

These bits set the duration of MAM Flash fetch operations as follows:

0 0 0 = 0 - Reserved.

0 0 1 = 1 - MAM fetch cycles are 1 processor clock (cclk) in duration.

0 1 0 = 2 - MAM fetch cycles are 2 processor clocks (cclks) in duration.

0 1 1 = 3 - MAM fetch cycles are 3 processor clocks (cclks) in duration.

1 0 0 = 4 - MAM fetch cycles are 4 processor clocks (cclks) in duration.

1 0 1 = 5 - MAM fetch cycles are 5 processor clocks (cclks) in duration.

1 1 0 = 6 - MAM fetch cycles are 6 processor clocks (cclks) in duration.

1 1 1 = 7 - MAM fetch cycles are 7 processor clocks (cclks) in duration.

Warning: Improper setting of this value may result in incorrect operation of the device.

0x07

7:3 Reserved

Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Loading...

Loading...