Vectored Interrupt Controller (VIC) 102 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

Vector Address Register (VICVectAddr - 0xFFFFF030, Read/Write)

When an IRQ interrupt occurs, the IRQ service routine can read this register and jump to the value read.

Protection Enable Register (VICProtection - 0xFFFFF020, Read/Write)

This one-bit register controls access to the VIC registers by software running in User mode.

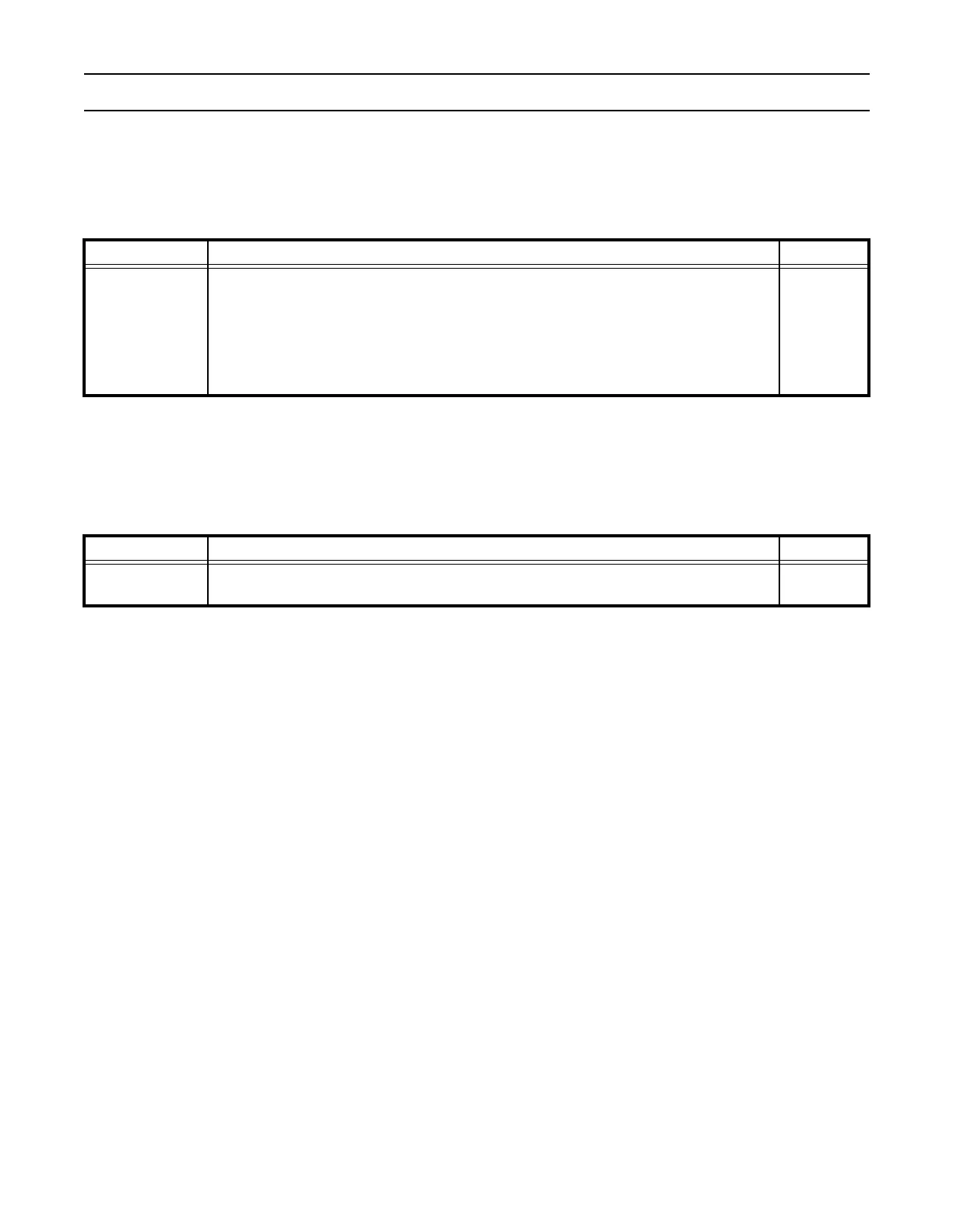

Table 52: Vector Address Register (VICVectAddr - 0xFFFFF030, Read/Write)

VICVectAddr Function Reset Value

31:0

If any of the interrupt requests or software interrupts that are assigned to a vectored IRQ slot

is (are) enabled, classified as IRQ, and asserted, reading from this register returns the

address in the Vector Address Register for the highest-priority such slot (lowest-numbered)

such slot. Otherwise it returns the address in the Default Vector Address Register.

Writing to this register does not set the value for future reads from it. Rather, this register

should be written near the end of an ISR, to update the priority hardware.

0

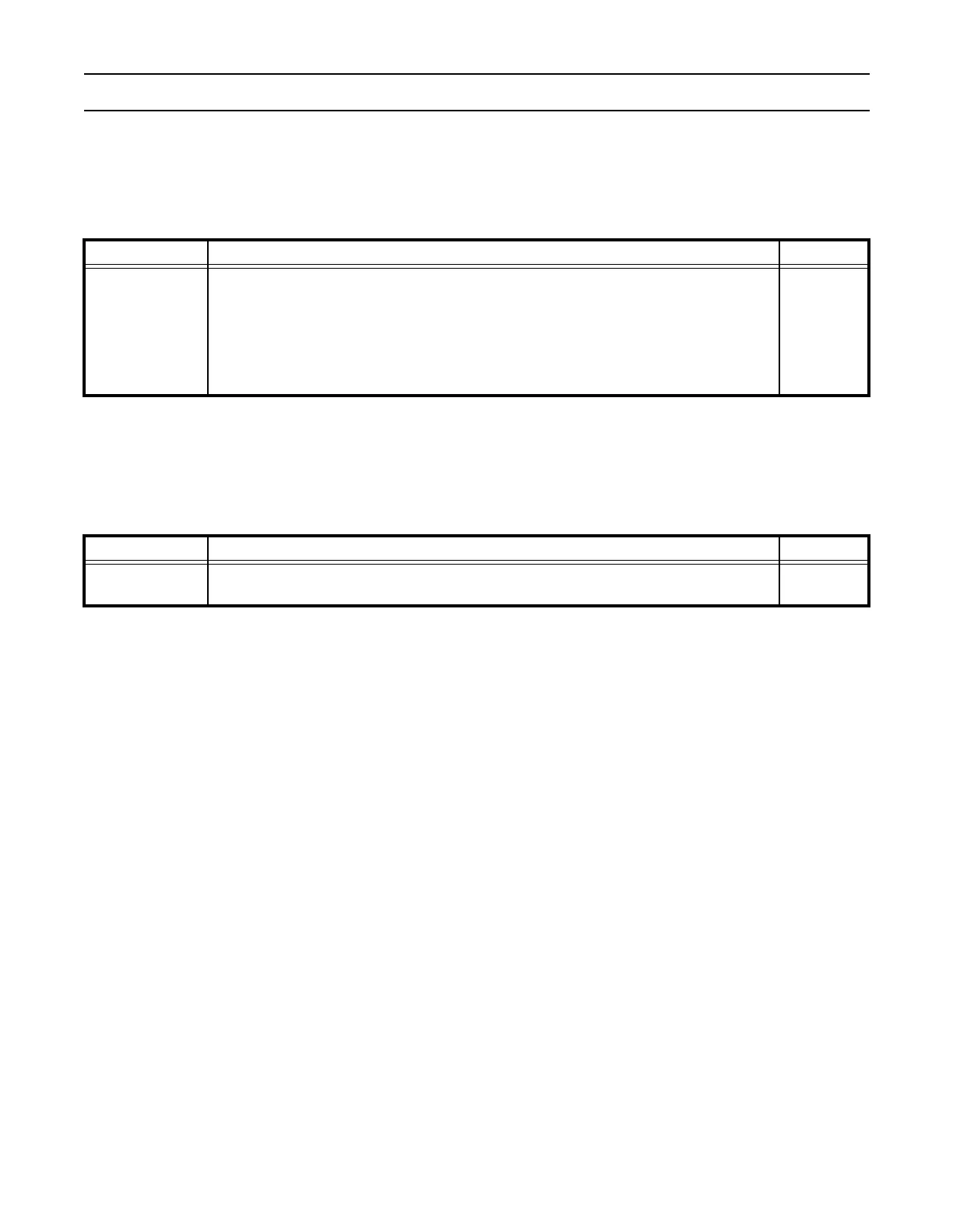

Table 53: Protection Enable Register (VICProtection - 0xFFFFF020, Read/Write)

VICProtection Function Reset Value

0

1: the VIC registers can only be accessed in privileged mode.

0: VIC registers can be accessed in User or privileged mode.

0

Loading...

Loading...