SPI Interface 184 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

SPI Status Register (S0SPSR - 0xE0020004, S1SPSR - 0xE0030004)

The SPSR register controls the operation of the SPI as per the configuration bits setting.

SPI Data Register (S0SPDR - 0xE0020008, S1SPDR - 0xE0030008)

This bi-directional data register provides the transmit and receive data for the SPI. Transmit data is provided to the SPI by writing

to this register. Data received by the SPI can be read from this register. When a master, a write to this register will start a SPI

data transfer. Writes to this register will be blocked from when a data transfer starts to when the SPIF status bit is set, and the

status register has not been read

.

SPI Clock Counter Register (S0SPCCR - 0xE002000C, S1SPCCR - 0xE003000C)

This register controls the frequency of a master’s SCK. The register indicates the number of pclk cycles that make up an SPI

clock. The value of this register must always be an even number. As a result, bit 0 must always be 0. The value of the register

must also always be greater than or equal to 8. Violations of this can result in unpredictable behavior.

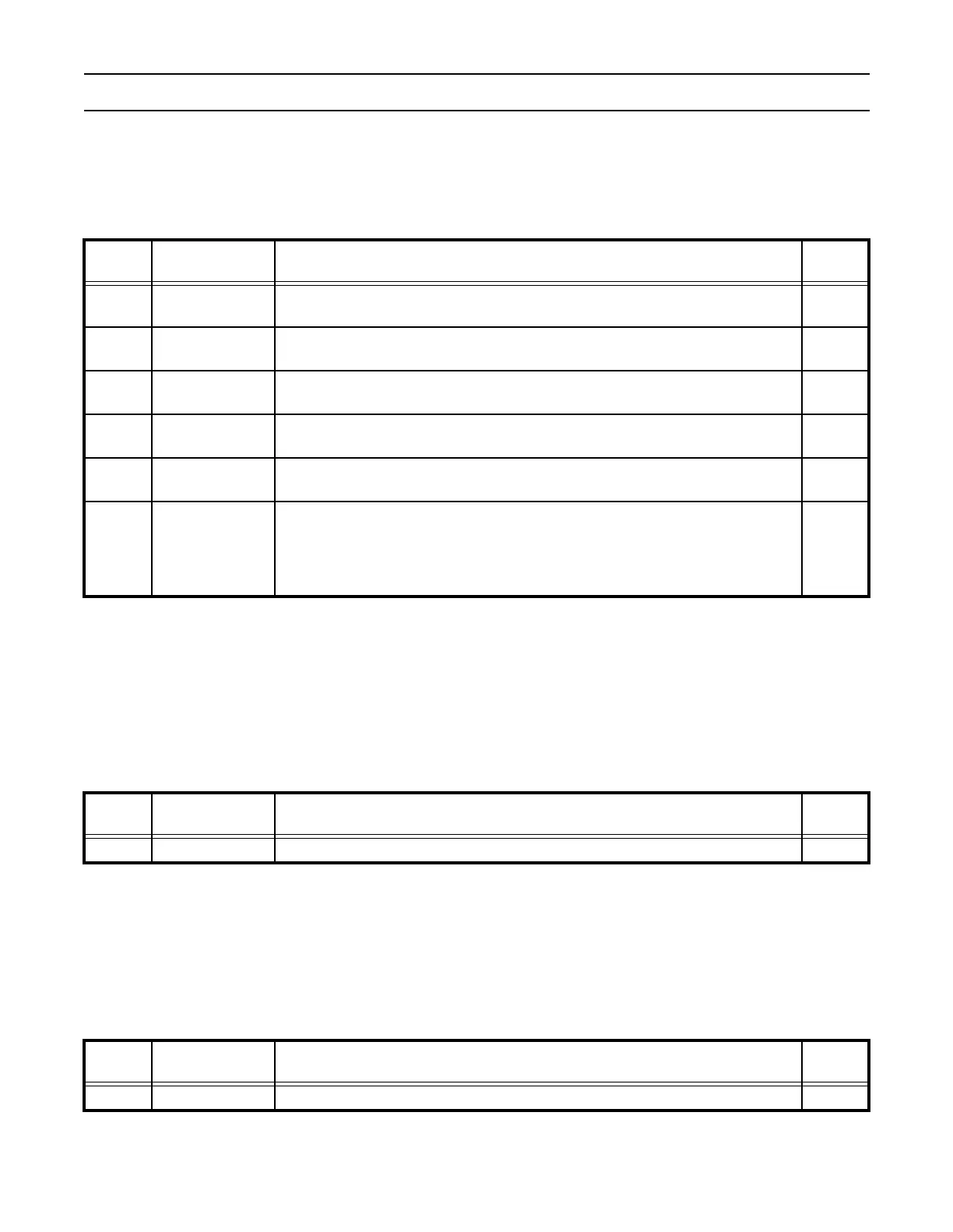

Table 117: SPI Status Register (S0SPSR - 0xE0020004, S1SPSR - 0xE0030004)

SPSR Function Description

Reset

Value

2:0 Reserved

Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

3 ABRT

Slave abort.

When 1, this bit indicates that a slave abort has occurred. This

bit is cleared by reading this register.

0

4MODF

Mode fault. when 1, this bit indicates that a Mode fault error has occurred. This bit is

cleared by reading this register, then writing the SPI control register.

0

5ROVR

Read overrun. When 1, this bit indicates that a read overrun has occurred. This bit is

cleared by reading this register.

0

6WCOL

Write collision. When 1, this bit indicates that a write collision has occurred. This bit

is cleared by reading this register, then accessing the SPI data register.

0

7 SPIF

SPI transfer complete flag. When 1, this bit indicates when a SPI data transfer is

complete. When a master, this bit is set at the end of the last cycle of the transfer.

When a slave, this bit is set on the last data sampling edge of the SCK. This bit is

cleared by first reading this register, then accessing the SPI data register.

Note: this is not the SPI interrupt flag. This flag is found in the SPINT registrer.

0

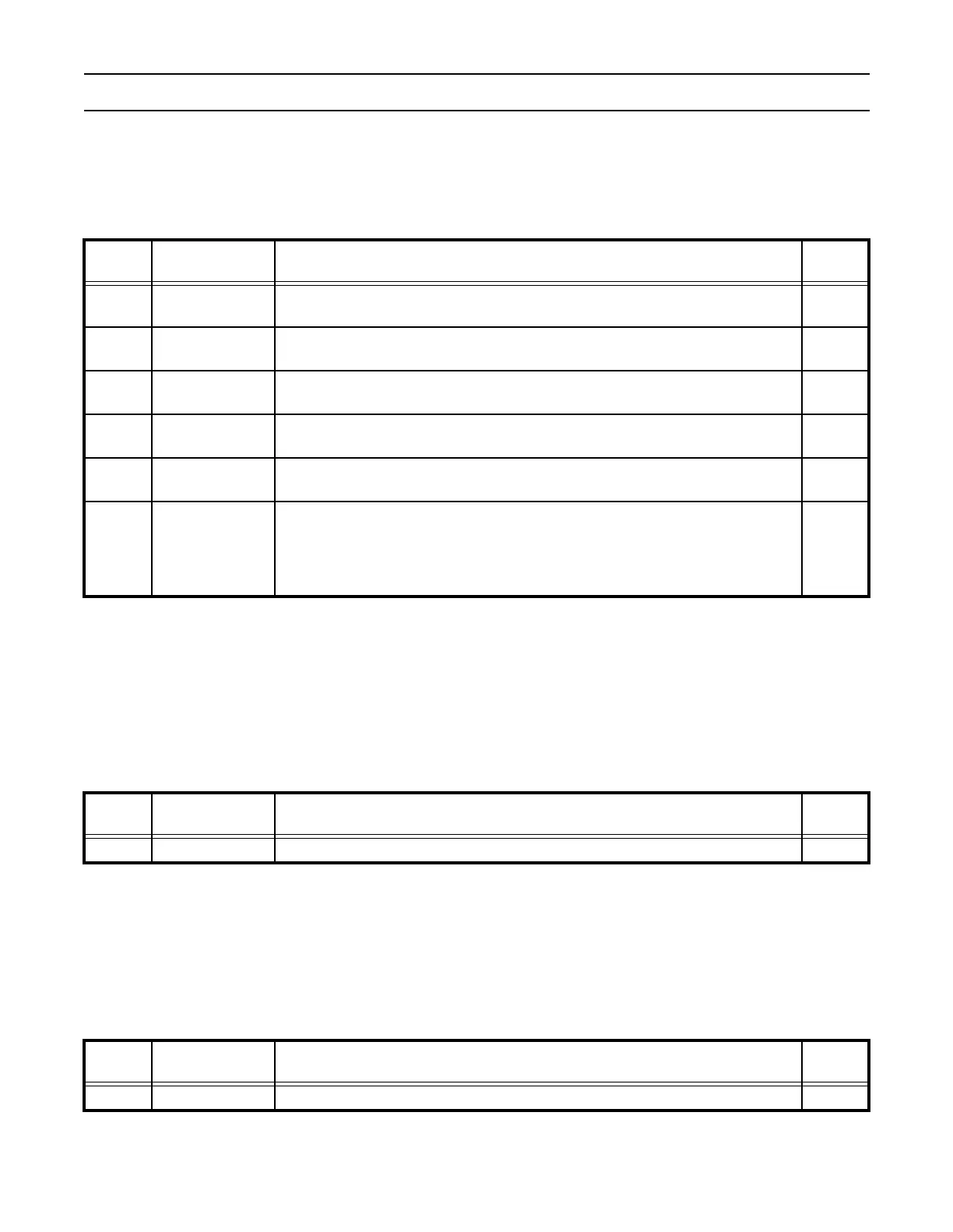

Table 118: SPI Data Register (S0SPDR - 0xE0020008, S1SPDR - 0xE0030008)

SPDR Function Description

Reset

Value

7:0 Data SPI Bi-directional data port 0

Table 119: SPI Clock Counter Register (S0SPCCR - 0xE002000C, S1SPCCR - 0xE003000C)

SPCCR Function Description

Reset

Value

7:0 Counter SPI Clock counter setting 0

Loading...

Loading...