UART0 141 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

REGISTER DESCRIPTION

*Reset Value refers to the data stored in used bits only. It does not include reserved bits content.

UART0 contains ten 8-bit registers as shown in Table 74. The Divisor Latch Access Bit (DLAB) is contained in U0LCR7 and

enables access to the Divisor Latches.

UART0 Receiver Buffer Register (U0RBR - 0xE000C000 when DLAB = 0, Read Only)

The U0RBR is the top byte of the UART0 Rx FIFO. The top byte of the Rx FIFO contains the oldest character received and can

be read via the bus interface. The LSB (bit 0) represents the “oldest” received data bit. If the character received is less than 8

bits, the unused MSBs are padded with zeroes.

The Divisor Latch Access Bit (DLAB) in U0LCR must be zero in order to access the U0RBR. The U0RBR is always Read Only.

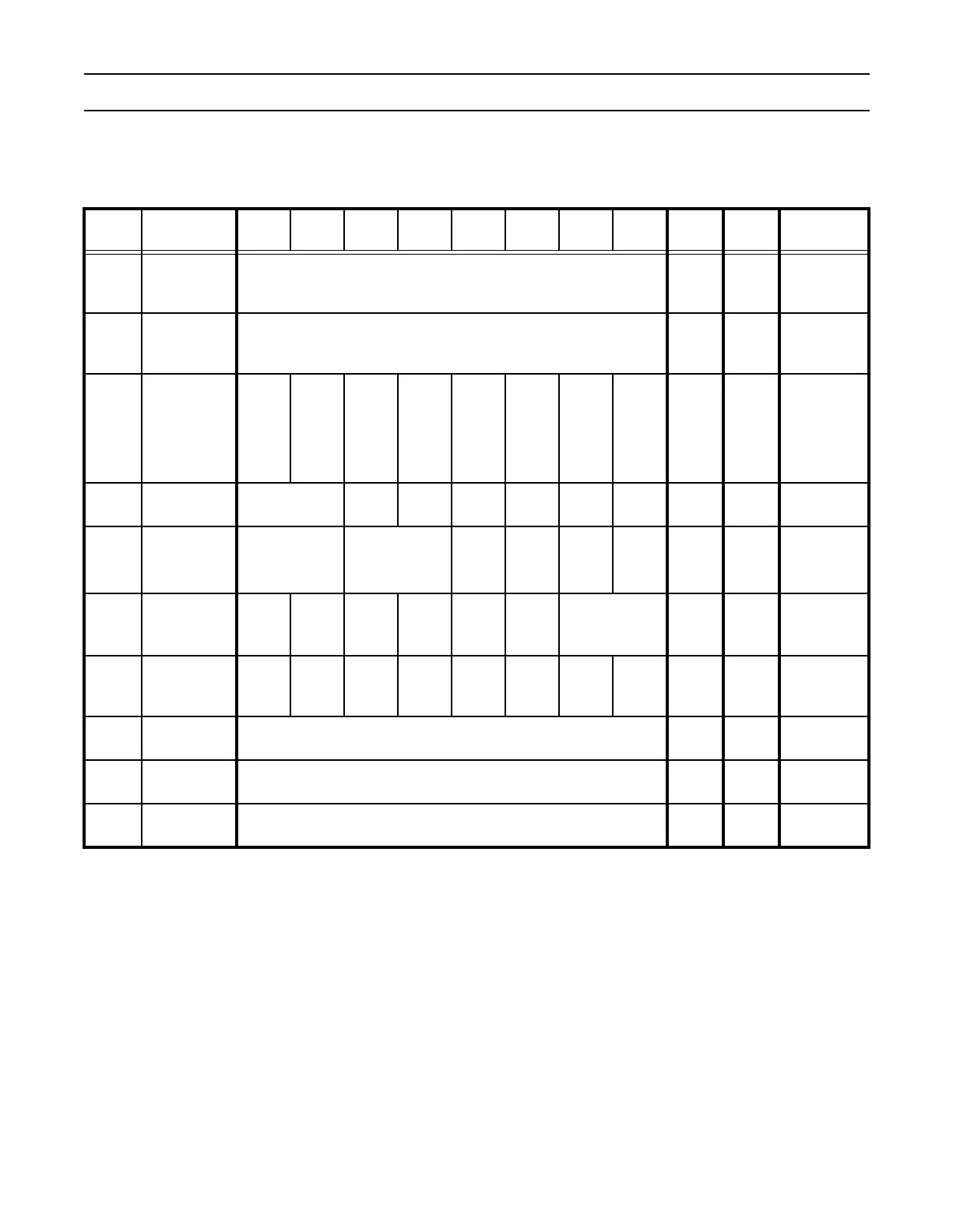

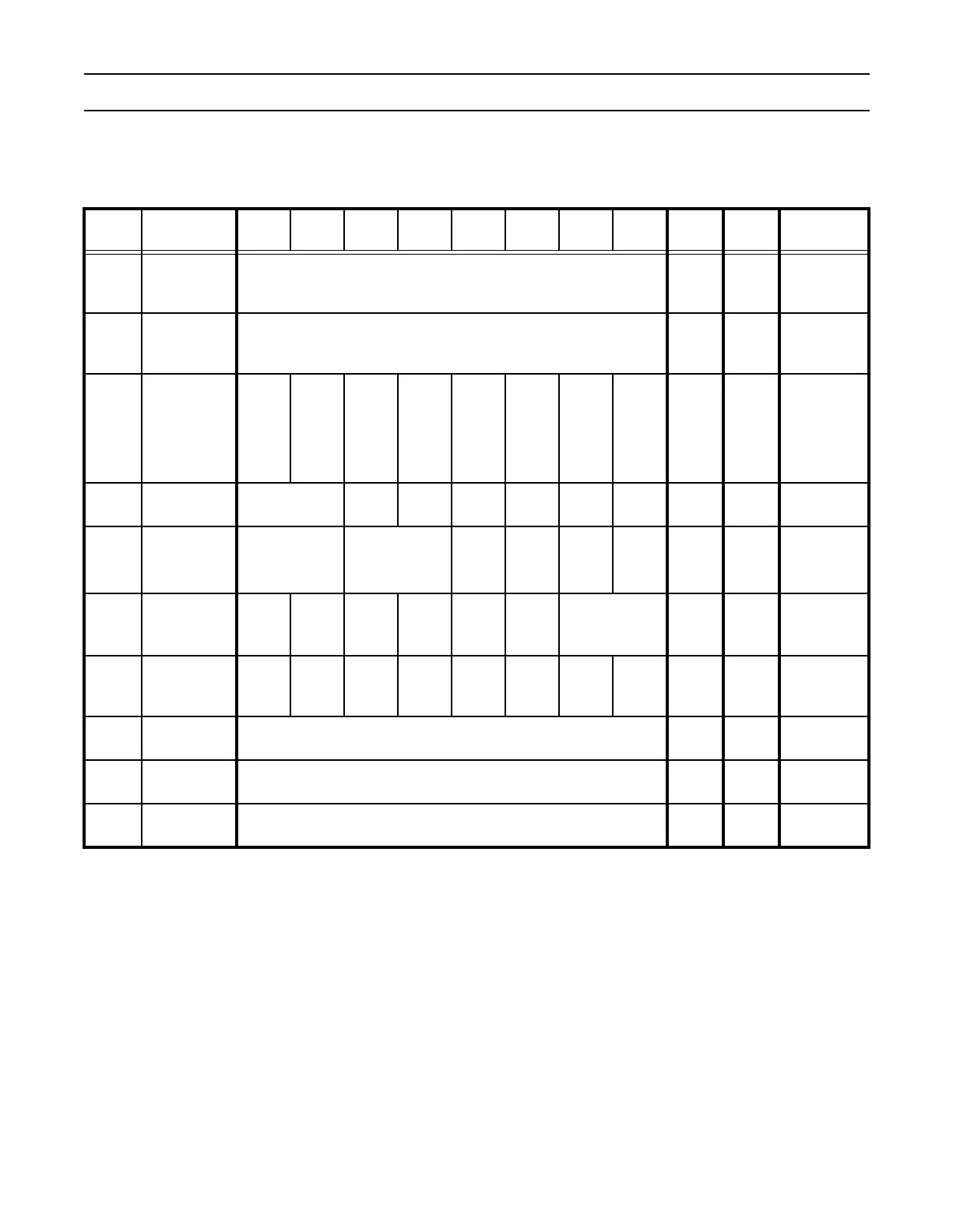

Table 74: UART0 Register Map

Name Description BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 Access

Reset

Value*

Address

U0RBR

Receiver

Buffer

Register

MSB READ DATA LSB RO

un-

defined

0xE000C000

DLAB = 0

U0THR

Transmit

Holding

Register

MSB WRITE DATA LSB WO NA

0xE000C000

DLAB = 0

U0IER

Interrupt

Enable

Register

00000

Enable Rx Line

Status

Interrupt

Enable THRE

Interrupt

Enable Rx Data

Available

Interrupt

R/W 0

0xE000C004

DLAB = 0

U0IIR

Interrupt ID

Register

FIFOs Enabled 0 0 IIR3 IIR2 IIR1 IIR0 RO 0x01 0xE000C008

U0FCR

FIFO

Control

Register

Rx Trigger Reserved -

Tx FIFO

Reset

Rx FIFO

Reset

FIFO

Enable

WO 0 0xE000C008

U0LCR

Line Control

Register

DLAB

Set

Break

Stick

Parity

Even

Parity

Select

Parity

Enable

Number

of Stop

Bits

Word Length

Select

R/W 0 0xE000C00C

U0LSR

Line Status

Register

Rx

FIFO

Error

TEMT THRE BI FE PE OE DR RO 0x60 0xE000C014

U0SCR

Scratch Pad

Register

MSB LSB R/W 0 0xE000C01C

U0DLL

Divisor Latch

LSB

MSB LSB R/W 0x01

0xE000C000

DLAB = 1

U0DLM

Divisor Latch

MSB

MSB LSB R/W 0

0xE000C004

DLAB = 1

Loading...

Loading...