EmbeddedICE Logic 288 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

REGISTER DESCRIPTION

The EmbeddedICE logic contains 16 registers as shown in Table 224. below. The ARM7TDMI-S debug architecture is described

in detail in "ARM7TDMI-S (rev 4) Technical Reference Manual" (ARM DDI 0234A) published by ARM Limited and is available via

Internet at http://www.arm.com.

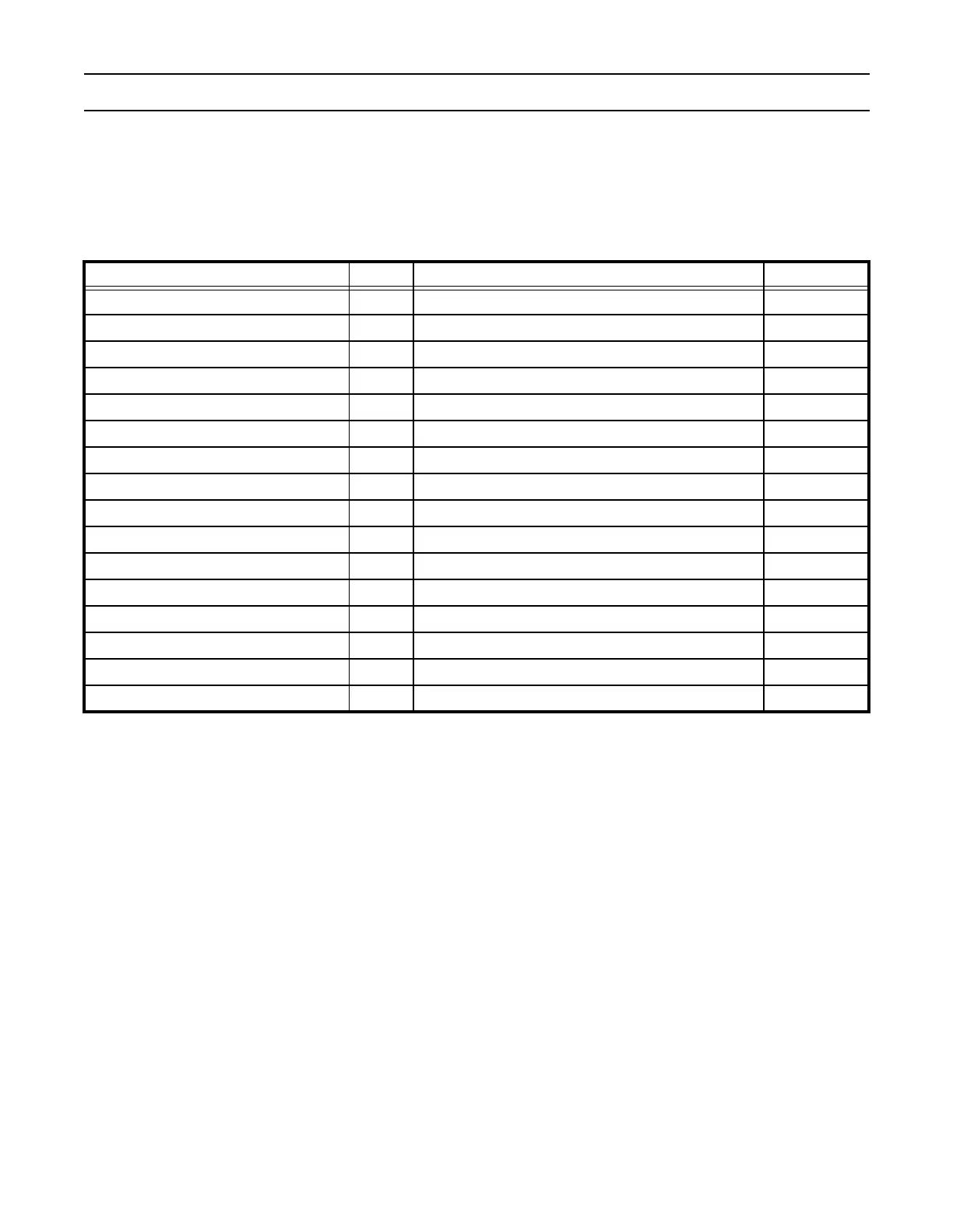

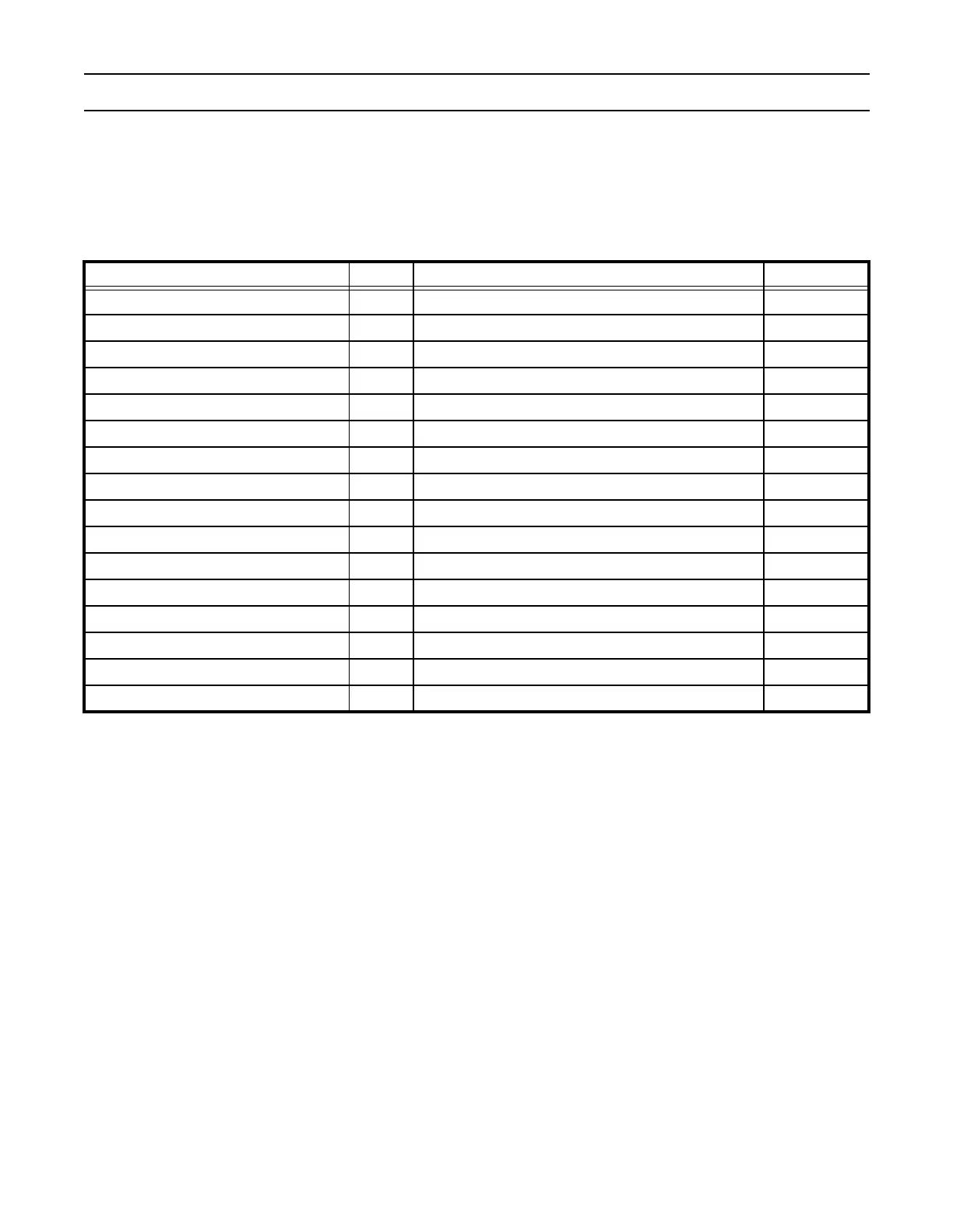

Table 224: EmbeddedICE Logic Registers

Name Width Description Address

Debug Control 6 Force debug state, disable interrupts 00000

Debug Status 5 Status of debug 00001

Debug Comms Control Register 32 Debug communication control register 00100

Debug Comms Data Register 32 Debug communication data register 00101

Watchpoint 0 Address Value 32 Holds watchpoint 0 address value 01000

Watchpoint 0 Address Mask 32 Holds watchpoint 0 address mask 01001

Watchpoint 0 Data Value 32 Holds watchpoint 0 data value 01010

Watchpoint 0 Data Mask 32 Holds watchpoint 0 data Mask 01011

Watchpoint 0 Control Value 9 Holds watchpoint 0 control value 01100

Watchpoint 0 Control Mask 8 Holds watchpoint 0 control mask 01101

Watchpoint 1 Address Value 32 Holds watchpoint 1 address value 10000

Watchpoint 1 Address Mask 32 Holds watchpoint 1 address mask 10001

Watchpoint 1 Data Value 32 Holds watchpoint 1 data value 10010

Watchpoint 1 Data Mask 32 Holds watchpoint 1 data Mask 10011

Watchpoint 1 Control Value 9 Holds watchpoint 1 control value 10100

Watchpoint 1 Control Mask 8 Holds watchpoint 1 control mask 10101

Loading...

Loading...